Array

(

[content] =>

[params] => Array

(

[0] => /forum/whats-new/latest-activity?before_id=107835

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2030970

[XFI] => 1060170

)

[wordpress] => /var/www/html

)

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today !

JavaScript is disabled. For a better experience, please enable JavaScript in your browser before proceeding.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an

alternative browser .

I would like to point out few things

- Intel has traditionally used HP Cells in their Products. Intel 10nm -> ADL,RPL,TGL Intel 4/3 ->...

Feb 21, 2026

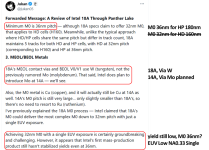

Some key Panther Lake design rules were posted on X:

Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from...

Feb 21, 2026

S

Well NVL is mix of 18AP/N2for compute tiles

I remember the issue being parametric not the D0 the D0 has been decent from what i know

Feb 21, 2026

M

Sam now says OpenAI's spend will be $600B, not $1.4T anymore. What do you think, is this reset expected, or a huge nasty surprise?

Key...

Feb 21, 2026

M

Tariffs was like 3 or 4 crises ago, they served their purpose for insider trading and now we can move on to the next charade.

Feb 21, 2026

L

I think the article want to point out that even under HP cell the yield is still not high, so the HD cell with smaller pitch may get...

Feb 21, 2026

F

If Backside or GAA/RibbonFET are new sources of yield loss, then relaxing to 36 nm pitch looks understandable. That said, high defect...

Feb 21, 2026

S

Feels like the last point is nonsense the decision to use HP/HD lies solely on the product group and their needs

Feb 21, 2026

F

So is the HD cell more difficult to fabricate than HP cell? Due to the smaller pitch dimensions?

Feb 21, 2026

F

yeah smaller dimensions are more work especially 32nm single print

Feb 21, 2026

N

Some key Panther Lake design rules were posted on X:

Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from...

Feb 21, 2026

E

Yeah but initial 18A PDKs had issues which caused the delay.

Feb 21, 2026

S

Yeah but initial 18A PDKs had issues which caused the delay.

Feb 21, 2026

Xebec reacted to siliconbruh999's post in the thread Panther Lake design rules revealed, no HD cells with

Xebec reacted to siliconbruh999's post in the thread Panther Lake design rules revealed, no HD cells with Like.

I would like to point out few things - Intel has traditionally used HP Cells in their Products. Intel 10nm -> ADL,RPL,TGL Intel 4/3 ->...

Like.

I would like to point out few things - Intel has traditionally used HP Cells in their Products. Intel 10nm -> ADL,RPL,TGL Intel 4/3 ->... Xebec reacted to Fred Chen's post in the thread Panther Lake design rules revealed, no HD cells with

Xebec reacted to Fred Chen's post in the thread Panther Lake design rules revealed, no HD cells with Like.

Some key Panther Lake design rules were posted on X: Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from...

Like.

Some key Panther Lake design rules were posted on X: Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from... Like.

Tariffs was like 3 or 4 crises ago, they served their purpose for insider trading and now we can move on to the next charade.

Like.

Tariffs was like 3 or 4 crises ago, they served their purpose for insider trading and now we can move on to the next charade. Like.

So is the HD cell more difficult to fabricate than HP cell? Due to the smaller pitch dimensions?

Like.

So is the HD cell more difficult to fabricate than HP cell? Due to the smaller pitch dimensions? Like.

Like.

Like.

yeah smaller dimensions are more work especially 32nm single print

Like.

yeah smaller dimensions are more work especially 32nm single print Like.

Some key Panther Lake design rules were posted on X: Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from...

Like.

Some key Panther Lake design rules were posted on X: Minimum pitch 36 nm (7nm-class), density obviously helped by 5 tracks from... Like.

Yeah but initial 18A PDKs had issues which caused the delay.

Like.

Yeah but initial 18A PDKs had issues which caused the delay.