Array

(

[content] =>

[params] => Array

(

[0] => /forum/whats-new/latest-activity?before_id=103239

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2030770

[XFI] => 1060170

)

[wordpress] => /var/www/html

)

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today !

JavaScript is disabled. For a better experience, please enable JavaScript in your browser before proceeding.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an

alternative browser .

S

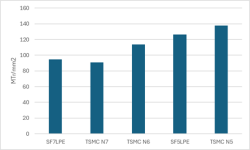

first thing requires reverse engineering and second thing i have seen a source for it but it's only for fewer comparison

Dec 13, 2025

F

Actually TSMC N7 to N5 M2 pitch shrink (40 nm to 35 nm) wasn't enough by itself to justify a node change. Gate pitch shrink was also...

Dec 13, 2025

F

TSMC N6 changed diffusion break from double to single, that in itself is enough to put it above 100 MTr/mm2. So it is a noticeable jump...

Dec 13, 2025

L

It seems like N+3 is truly G57H228 ( come from Techinsight decap data).

Hard to judge whether this is 5nm or not.

Techinsight think...

Dec 13, 2025

K

Great list - would be interesting to look at number of transistors and rough power / performance curve of each core.

Dec 13, 2025

A sheet with core sizes of CPU Cores

https://docs.google.com/spreadsheets/d/1r_RGcH02hcM2p-UYIbJFBJ_vJYrwtdC7w1dWXda0iwI/edit?gid=0#gid=0

Dec 13, 2025

D

N2 elvt threhold is around 0.1v.

The real trick is leakage.

Most btc mining chips are using dynamic logic which are almost impossible...

Dec 13, 2025

You heard it here first: AMD $AMD is planning to use Intel $INTC foundry to manufacture chips in the USA (not just packaging). During my...

Dec 13, 2025

Daniel Nenni replied to the thread

PAX SILICA .

What is Pax Silica?

We affirm our shared commitment to advance mutual prosperity, technological progress, and economic security for...

Dec 13, 2025

S

interesting. i thought bit mining is mainly performance driven. Lowering vdd to 0.25v using existing leading edge means they are all...

Dec 13, 2025

S

BTC mining chips .

TSMC N3P and N2.

Dec 13, 2025

S

CNBC Marathon investigates the intricate, high-stakes world of semiconductor manufacturing from the Dutch labs powering AI chip...

Dec 13, 2025

Also, please don't think the fab is the only piece of this puzzle.

After the fab:

Probe wafer test

Slice and package

Package test

Burn...

Dec 13, 2025

D

BTC mining chips .

TSMC N3P and N2.

Dec 13, 2025

S

not familiar with this. What application and process?

Dec 13, 2025

Xebec reacted to siliconbruh999's post in the thread Core Size Info from CPU Cores from Intel/AMD/Apple/MTK/QCOM with

Xebec reacted to siliconbruh999's post in the thread Core Size Info from CPU Cores from Intel/AMD/Apple/MTK/QCOM with Like.

A sheet with core sizes of CPU Cores https://docs.google.com/spreadsheets/d/1r_RGcH02hcM2p-UYIbJFBJ_vJYrwtdC7w1dWXda0iwI/edit?gid=0#gid=0

Like.

A sheet with core sizes of CPU Cores https://docs.google.com/spreadsheets/d/1r_RGcH02hcM2p-UYIbJFBJ_vJYrwtdC7w1dWXda0iwI/edit?gid=0#gid=0 Daniel Nenni posted the thread AMD Job Listing Suggests Partnership with Intel Foundry in SemiWiki Main Forum ( Ask the Experts! ).You heard it here first: AMD $AMD is planning to use Intel $INTC foundry to manufacture chips in the USA (not just packaging). During my...

Daniel Nenni posted the thread AMD Job Listing Suggests Partnership with Intel Foundry in SemiWiki Main Forum ( Ask the Experts! ).You heard it here first: AMD $AMD is planning to use Intel $INTC foundry to manufacture chips in the USA (not just packaging). During my... Daniel Nenni replied to the thread PAX SILICA.What is Pax Silica? We affirm our shared commitment to advance mutual prosperity, technological progress, and economic security for...

Daniel Nenni replied to the thread PAX SILICA.What is Pax Silica? We affirm our shared commitment to advance mutual prosperity, technological progress, and economic security for... Like.

BTC mining chips . TSMC N3P and N2.

Like.

BTC mining chips . TSMC N3P and N2. Xebec reacted to Dougwithau's post in the thread How "fungible" are memory maker fabs for switching between memory types? with

Xebec reacted to Dougwithau's post in the thread How "fungible" are memory maker fabs for switching between memory types? with Like.

Also, please don't think the fab is the only piece of this puzzle. After the fab: Probe wafer test Slice and package Package test Burn...

Like.

Also, please don't think the fab is the only piece of this puzzle. After the fab: Probe wafer test Slice and package Package test Burn...