Array

(

[content] =>

[params] => Array

(

[0] => /forum/whats-new/latest-activity?before_id=103188

)

[addOns] => Array

(

[DL6/MLTP] => 13

[Hampel/TimeZoneDebug] => 1000070

[SV/ChangePostDate] => 2010200

[SemiWiki/Newsletter] => 1000010

[SemiWiki/WPMenu] => 1000010

[SemiWiki/XPressExtend] => 1000010

[ThemeHouse/XLink] => 1000970

[ThemeHouse/XPress] => 1010570

[XF] => 2030770

[XFI] => 1060170

)

[wordpress] => /var/www/html

)

You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today !

JavaScript is disabled. For a better experience, please enable JavaScript in your browser before proceeding.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an

alternative browser .

It’s interesting that Rivian is getting into the AI chip business and appears to be targeting industries more than just automotive...

Dec 13, 2025

I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE...

Dec 13, 2025

I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE...

Dec 13, 2025

M

Not being a formal news, rumors from private network said ASML was forced to pending JSMC EUV delivery indefinitely for some...

Dec 13, 2025

S

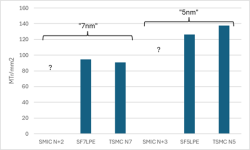

Node shrink will continue to matter than cause while density benefits have been lowered but Power and performance still continue to scale

Dec 13, 2025

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime...

Dec 13, 2025

F

Appreciate all the discussion and accurate numbers on minimum pitches and raw maximum cell densities, but without any discussion of...

Dec 12, 2025

F

I'd picture it this way...

Dec 12, 2025

L

118mtr is my guess.

By the way, a Chinese forum post an information, not sure if this is true.

He mention that N+3 gate pitch is 57nm...

Dec 12, 2025

J

you dont recover glory. The gain new glory.

Intel was a dominant execution engine in the past with no competitor who could succeed...

Dec 12, 2025

J

Are they using some new ultra high density library?

Dec 12, 2025

J

N+2 is 93 mtr.

It has 63nm gate pitch and 252nm cell height which revealed by Techinsight.

118 mtr mean ~27% density improve, very huge.

Dec 12, 2025

S

I suspect that quantum computing will blow the current state of the art semiconductor technology and optical computing out of the water...

Dec 12, 2025

S

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime...

Dec 12, 2025

S

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package...

Dec 12, 2025

hist78 replied to the thread Rivian (auto company) has a custom 5nm chip now too - RAP1.It’s interesting that Rivian is getting into the AI chip business and appears to be targeting industries more than just automotive...

hist78 replied to the thread Rivian (auto company) has a custom 5nm chip now too - RAP1.It’s interesting that Rivian is getting into the AI chip business and appears to be targeting industries more than just automotive... hist78 reacted to Xebec's post in the thread Rivian (auto company) has a custom 5nm chip now too - RAP1 with

hist78 reacted to Xebec's post in the thread Rivian (auto company) has a custom 5nm chip now too - RAP1 with Like.

I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE...

Like.

I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE... Xebec posted the thread Rivian (auto company) has a custom 5nm chip now too - RAP1 in SemiWiki Main Forum ( Ask the Experts! ).I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE...

Xebec posted the thread Rivian (auto company) has a custom 5nm chip now too - RAP1 in SemiWiki Main Forum ( Ask the Experts! ).I think it is great to see another automotive company leveraging an advanced node (5nm). The chip appears to have 14 x Cortex A720AE... Xebec reacted to Scotten Jones's post in the thread How "fungible" are memory maker fabs for switching between memory types? with

Xebec reacted to Scotten Jones's post in the thread How "fungible" are memory maker fabs for switching between memory types? with Like.

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime...

Like.

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime... Like.

Appreciate all the discussion and accurate numbers on minimum pitches and raw maximum cell densities, but without any discussion of...

Like.

Appreciate all the discussion and accurate numbers on minimum pitches and raw maximum cell densities, but without any discussion of... Like.

you dont recover glory. The gain new glory. Intel was a dominant execution engine in the past with no competitor who could succeed...

Like.

you dont recover glory. The gain new glory. Intel was a dominant execution engine in the past with no competitor who could succeed... Wow.

N+2 is 93 mtr. It has 63nm gate pitch and 252nm cell height which revealed by Techinsight. 118 mtr mean ~27% density improve, very huge.

Wow.

N+2 is 93 mtr. It has 63nm gate pitch and 252nm cell height which revealed by Techinsight. 118 mtr mean ~27% density improve, very huge. Like.

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime...

Like.

They all use the same fab process although HBM add TSVs - basically do a new design and run it through the fab. There is no downtime... Like.

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package...

Like.

Other than HBM they are similar. but the Chip designs are different so its a wafer start issue (Assume cycle time from start to package...