In the world of financial trading, nanoseconds count. The faster a trade can be accomplished, the more money a trader can make. Getting a trade in before a competitor also results in improved profits. What does this have to do with the partnership deal recently inked between Silicon Creations and Achronix? Plenty. The two companies… Read More

Creating Analog PLL IP for TSMC 5nm and 3nm

TSMC’s Open Innovation Platform’s main objective is to create and promote partnership for producing chips. This year’s OIP event included a presentation on the joint efforts of Silicon Creations, Mentor, a Siemens business and TSMC to produce essential PLL IP for 5nm and 3nm designs. The relentless push for smaller geometries… Read More

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

Keeping Pace With 5nm Heartbeat

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power… Read More

Context is Everything – especially for autonomous vehicle IP

GM has just announced that it will introduce a car with no steering wheel or pedals in 2019. According to their statement, they have already planned four phases of their autonomous driving system, and they will plan many more. However, before we jump into this latest car and not grab the wheel for a spin, it is reasonable to ask about… Read More

Safety qualification for leading edge IP elements – presentation at REUSE 2017 in Santa Clara

To ensure the reliability of automotive electronics, standards like AEC-Q100 and ISO 26262 have helped tremendously. They have created rational and explicit steps for developing and testing the electronic systems that go into our cars. These are not some abstract future requirement for fully autonomous cars, rather they are… Read More

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

Understanding Sources of Clock Jitter Critical for SOC’s

Jitter issues in SOC’s reside at the crossroads of analog and digital design. Digital designers would prefer to live in a world of clocks that are free from jitter effects. At the same time, analog designers can build PLL’s that are precise and finely tuned. However, when a perfectly working PLL is inserted into an SOC, things can … Read More

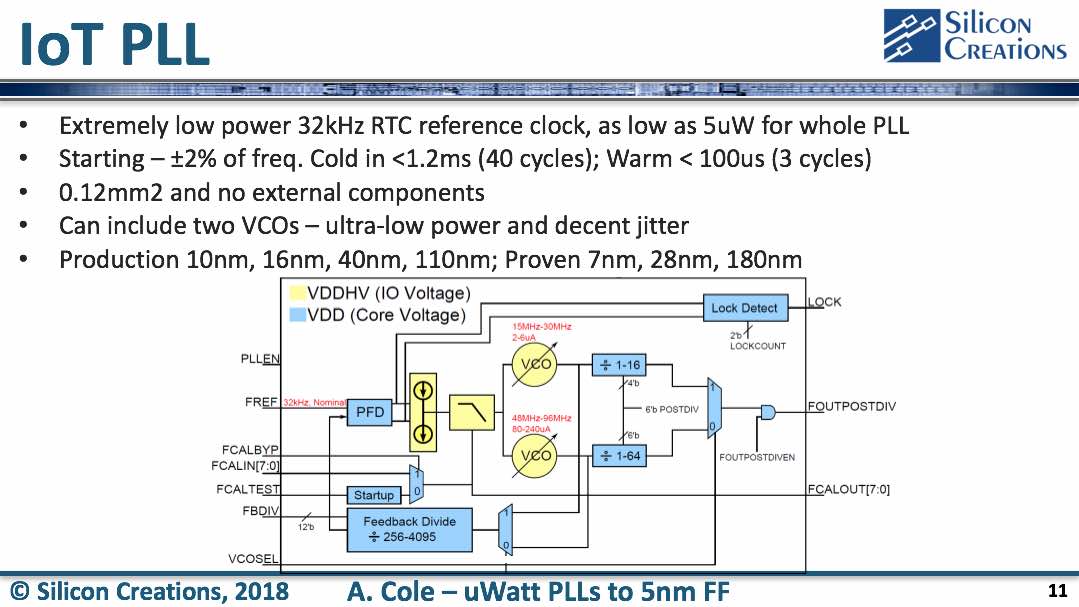

Who knew designing PLL’s was so complicated?

Well it comes as no surprise to those that use and design them, that PLL’s are a world unto themselves and very complicated indeed. With PLL’s we are talking about analog designs that rely on ring oscillators or LC tanks. They are needed on legacy nodes, like the ones that IoT chips are based on, and they are crucial for high speed advanced… Read More

CTO Interview: Jeff Galloway of Silicon Creations

It is clear that IP companies play an important role in modern semiconductor design, in fact, I would say that they are imperative. Founded in 2006, Silicon Creations is one of those imperative IP companies that provide silicon proven IP to customers big and small around the world. To follow-up on our conversation with Silicon Creations… Read More