GenAI, the most talked-about manifestation of AI these days, imposes two tough constraints on a hardware platform. First, it demands massive memory to serve large language model with billions of parameters. Feasible in principle for a processor plus big DRAM off-chip and perhaps for some inference applications but too slow … Read More

ASML- Soft revenues & Orders - But...China 49% - Memory ImprovingASML- better EPS but weaker revenues- 2024 recovery…Read More

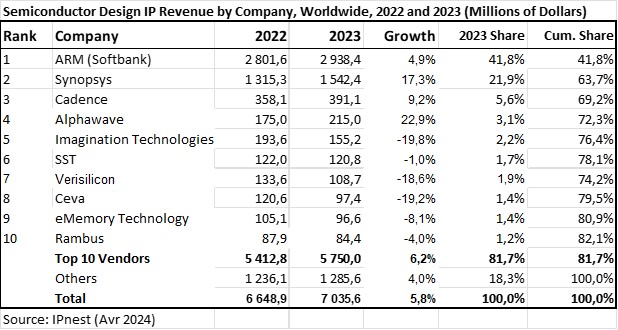

ASML- Soft revenues & Orders - But...China 49% - Memory ImprovingASML- better EPS but weaker revenues- 2024 recovery…Read More Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!Design IP revenues had achieved $7.04B in 2023,…Read More

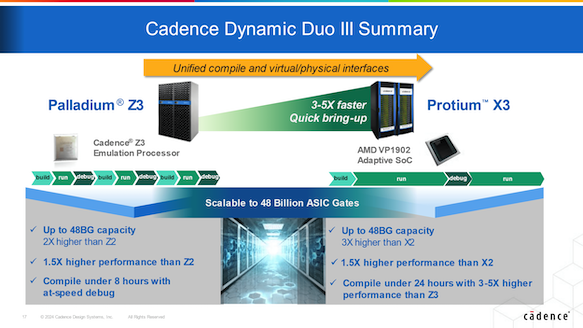

Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!Design IP revenues had achieved $7.04B in 2023,…Read More Cadence Debuts Dynamic Duo III with a Basket of GoodiesI am a fan of product releases which…Read More

Cadence Debuts Dynamic Duo III with a Basket of GoodiesI am a fan of product releases which…Read More CEO Interview: Khaled Maalej, VSORA Founder and CEOKhaled Maalej is founder and CEO of VSORA,…Read More

CEO Interview: Khaled Maalej, VSORA Founder and CEOKhaled Maalej is founder and CEO of VSORA,…Read MoreDesign Stage Verification Gives a Boost for IP Designers

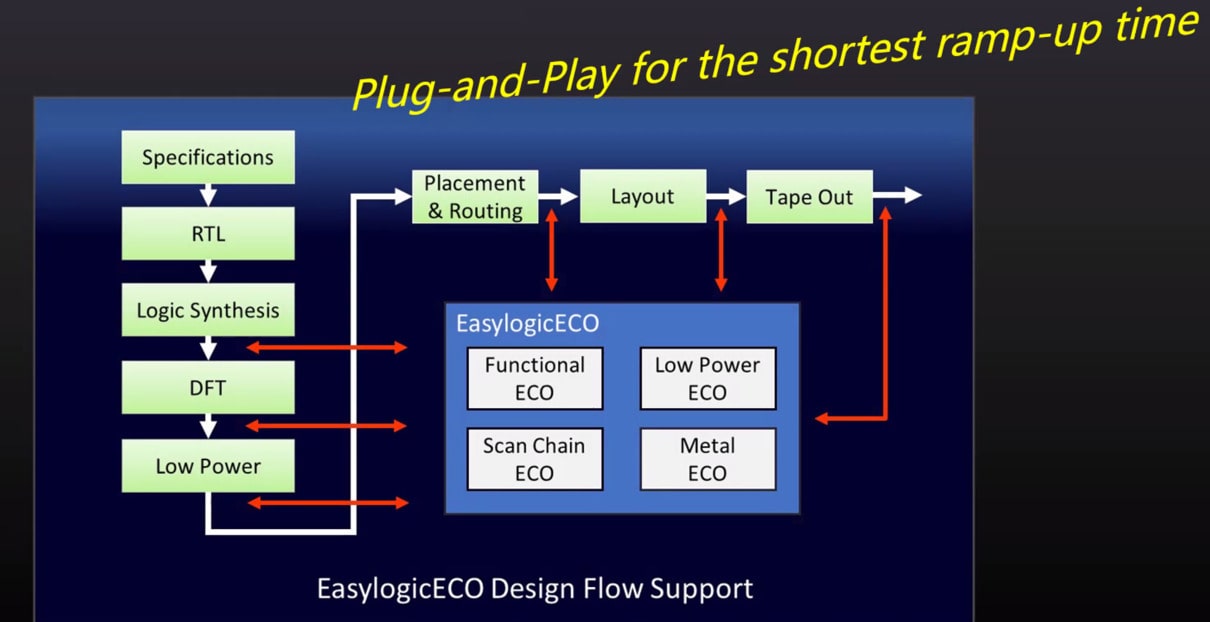

The concept of shift left is getting to be quite well-known. The strategy involves integrating various checks typically performed later in the design process into earlier stages. The main benefit is to catch and correct defects or errors at an earlier stage when it’s easier and faster to address. For complex SoC design, … Read More

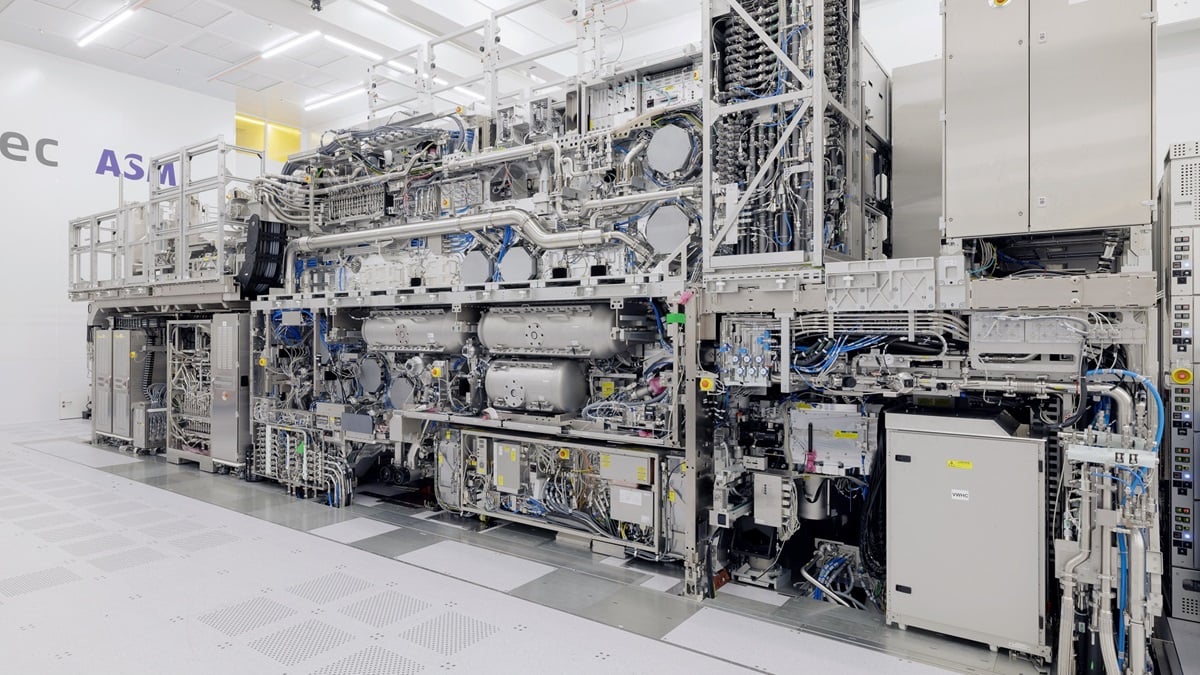

Intel High NA Adoption

On Friday April 12th Intel held a press briefing on their adoption of High NA EUV with Intel fellow and director of lithography Mark Phillips.

In 1976 Intel built Fab 4 in Oregon, the first Intel fab outside of California. With the introduction of 300mm Oregon became the only development site for Intel with large manufacturing, development,… Read More

Electronics Turns Positive

Unit shipments of both PCs and smartphones versus a year ago have turned positive. According to IDC, PC shipments in 1Q 2024 were up 1.5% from 1Q 2023, the first positive year-to-year change since 4Q 2021. Smartphone year-to-year growth turned positive in 4Q 2023 at 8.5%. The growth continued in 1Q 2024 at 7.8%. 4Q 2023 was the first… Read More

2024 Outlook with Ben Packman of PQShield

Ben Packman, Senior Vice President at PQShield, leads global expansion through sales and partner growth across multiple vertical markets, alongside taking a lead role in briefing both government and the supply chain on the quantum threat.

Tell us a little bit about yourself and your company.

PQShield is a post-quantum cryptography… Read More

Real men have fabs!

“Real men have fabs” was an insult AMD founder Jerry Sanders hurled at his poor competitors who could not afford to build fabs. A few years later, AMD would be fabless, spinning off its manufacturing facilities as GlobalFoundries. This was the beginning of a transformative period for the industry.

Lisa Su could rightfully retort:

Fault Sim on Multi-Core Arm Platform in China. Innovation in Verification

How much can running on a multi-core (Arm) CPU speed up fault simulation? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome.

The Innovation

Huawei’s and SMIC’s Requirement for 5nm Production: Improving Multipatterning Productivity

There has been much interest in Huawei’s and SMIC’s plans for 5nm production in the near future. Since there is no use of EUV in China, immersion DUV lithography (with a 76 nm pitch resolution) is expected to be used along with pitch quartering to achieve pitches in the 20-30 nm range expected for the 5nm and 3nm nodes [1].… Read More

How Secure-IC is Making the Cyber World a Safer Place

Securing the data and all the associated transactions that comprise our hyper-connected world is a daunting task. Security touches the hardware, software and all the channels connecting every device and every transaction. Threats can be embedded in software, hardware or systems can be compromised externally using a large … Read More

Not all Smartphones are Created Equal

TechInsights recognizes Earth Day 2024 by lifting the screen on smartphone semiconductor sustainability

Smartphones are typically compared based on screen size, processor speed, and camera resolution. But when TechInsights looked at carbon footprints for manufacturing just the semiconductors of three flagship phones,… Read More

Real men have fabs!