I was fortunate to have a 1-on-1 with Anirudh before he delivered the keynote at DVCon. In case you don’t know the name, Dr. Anirudh Devgan is Executive VP and GM of the Digital & Signoff Group and the System & Verification Group at Cadence. He’s on a meteoric rise in the company, not least for what he has done for Cadence’s position in verification in just a year.

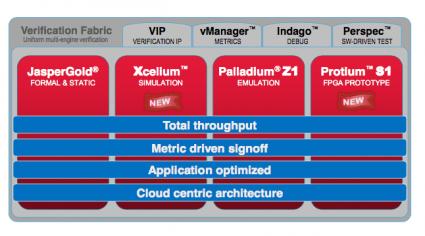

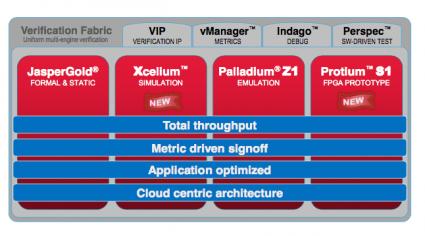

Of course, Cadence was never a slouch in verification. Back in the early 90’s they acquired Gateway, making them the sole provider of Verilog simulation for a while, they’ve got world-class engines in Jasper for formal and Palladium for emulation, but their simulation and prototyping products haven’t exactly towered over similar solutions in recent years. That changed at this year’s DVCon where they announced order of magnitude improvements in both platforms, which Anirudh asserts puts them at the top of the pack across all the verification engines.

That’s the most obvious change in the new Cadence verification lineup, but what’s the bigger picture? He uses a transportation analogy to explain this. When you buy something online, delivering that package to your doorstep requires two things – fast engines (planes, ships, trains and trucks) and smart logistics (optimizing use of these resources for fast and cost-effective store-to-door shipping). He sees verification in the same way – you need fast engines and you need a smart environment (logistics) to get you to verification signoff quickly and with high quality.

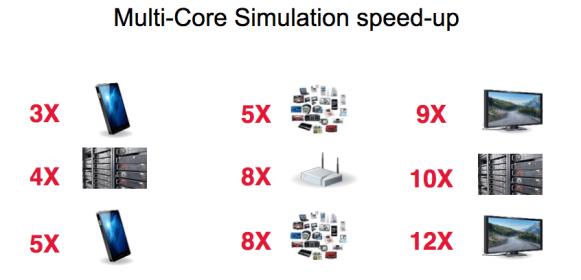

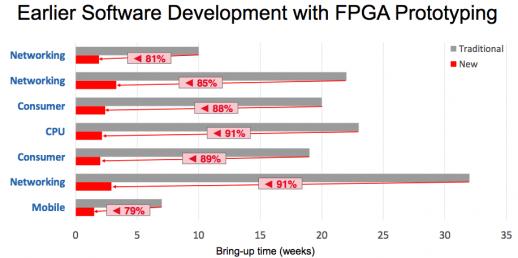

This starts, you’ll be happy to hear, with the fastest engines he can deliver at any given time; he doesn’t believe that you can build great solutions on top of average engines. And he’s unimpressed by incremental improvements. Tell him you’ve found a way to increase performance by 20% and you lose his interest. He wants to see order-of-magnitude improvements (maybe there’s something to this idea of putting an implementation guy in charge of verification). These priorities are very apparent in Xcelium simulation runtimes and Protium S1 bring-up improvements announced at this year’s DVCon.

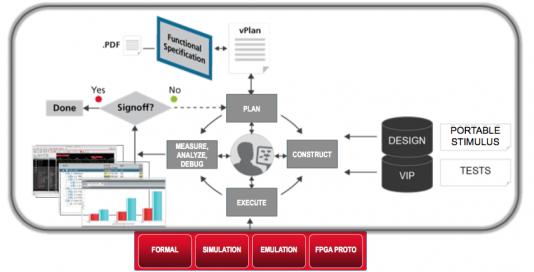

So, top-flight engines across the line, check. Anirudh then turned to the logistics part of the puzzle – a smart environment for verification. He sees this as being about:

- Total throughput. It’s not just about fast engines; the complete verification flow needs to be fast and efficient – planning, building tests, debugging errors and jumping around between engines to isolate problems. Cadence already offers vManager, comprehensive support for UVM and Indago to support many of these tasks. Cadence is also arguably the market leader in verification IP (including multi-engine support). A recent additional and important step along these lines is much tighter coupling between Palladium emulation and Protium S1 prototyping, enabling quick and easy modeling transfer between platforms.

- Knowing when you’re done. This requires metric-driven verification and signoff supported by high-productivity test generation and rich options in measuring coverage. vManager coupled with UVM coverage delivers the metrics. A recently publicized and very strong addition to this area is Perspec System Verifier for automated high-volume system-level test generation, which will get you to a higher quality “done” much faster.

- Application-optimized test, including support for features like mixed signal analysis for consumer and IoT, power analysis for mobile and IoT and safety and compliance analysis for automotive. Cadence offers multiple options in these areas.

- Elastic compute resources. Cloud access is a big part of this, both in secure public clouds and in private clouds. Palladium Z1 enterprise emulation platform is another part, providing virtual access to emulation power to a much wider user-base.

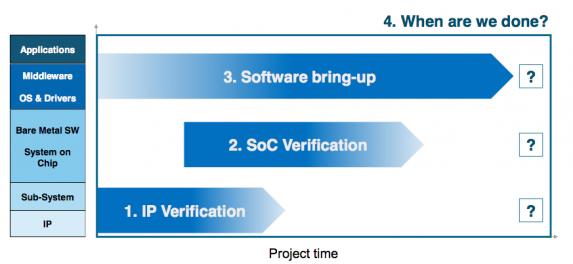

All great improvements, but how do they stack up against customer demands? Anirudh pointed out that a lot of emerging system-development teams don’t necessarily have the range of expertise found in big semiconductor companies. And they operate in organizations expecting that if everything is built on reusable IP, design to signoff (including verification) should be much faster. This drives four customer priorities per Anirudh (actually in reverse order to the picture above):

- When are we done? As mentioned earlier, vManager with planning and metrics has a big impact on this.

- Why can’t I start software development and debug in parallel with design? Protium S1 and tight integration with Palladium pull software development and debug much earlier in the design cycle and make it more accessible to system designers unskilled in the arcana of FPGA prototyping.

- Why does SoC design speed up with IP reuse, but not SoC verification? Perspec portable stimulus generation has an order of magnitude impact on test generation productivity and the portability of the approach promises to bring expectations for reuse in verification much closer to reality.

- Why isn’t IP testing more complete? Greater use of formal and easier/non-expert access through formal applications, coupled with directed and random simulation, offers more complete proofs especially for hard problems like security and cache coherence.

Where does Anirudh see opportunity going forward? Vendors are always cagey about futures, for competitive reasons and GAAP/SEC requirements, but he was willing to open up a little. First, he sees plenty of opportunity to reach for more order of magnitude improvements in engines. Again, he’s not hampered by what we experts “know” can’t be done. He believes in big parallelism, more completeness and more out-of-the-box approaches. There’s also more opportunity for ease of use. System designers have neither the time nor the patience to learn complex verification flows. He thinks more big gains are possible here.

Then of course there is opportunity for more intelligence, through Big Data analytics and machine learning (ML). When I asked him to elaborate, he grinned and said he couldn’t but did note that Cadence already has over a hundred ML experts. So I’m going to assume there will be announcements around this area at some point.

Cadence has an impressive verification story, not just in terms of completeness and performance, but also in positioning for new waves of systems designers. These guys (and particularly Anirudh) are going to be very interesting to watch.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.