You’d expect Mentor to be covering a lot of bases at DVCon and you wouldn’t be wrong. They’re hosting  tutorials, a lunch, papers, posters, there’s a panel and of course they’ll be on the exhibit floor. I’ll start with an important tutorial that you really should attend, Monday morning, on creating Portable Stimulus Models based on the PSS standard. I know verification engineers barely get time to think, much less look ahead but this one stands between you and more effective test generation, coverage and debug so you pretty much must deal with it. Mentor as a leader in defining the standard already has technology in this area so what you learn here can be valuable immediately.

tutorials, a lunch, papers, posters, there’s a panel and of course they’ll be on the exhibit floor. I’ll start with an important tutorial that you really should attend, Monday morning, on creating Portable Stimulus Models based on the PSS standard. I know verification engineers barely get time to think, much less look ahead but this one stands between you and more effective test generation, coverage and debug so you pretty much must deal with it. Mentor as a leader in defining the standard already has technology in this area so what you learn here can be valuable immediately.

Monday afternoon they have a speaker in a tutorial on SystemC (also featuring speakers from Intel, NXP and Coseda). SystemC is a curious beast – when viewed purely from the perspective of RTL and as a higher-level alternative to RTL, it looks a marginal player (maybe 10% of design). But when viewed from a broader perspective it becomes a lot more interesting. System-level designers (at Google for example) want a fast path from concept to silicon, see no need to fiddle with intermediate RTL and apparently see a high level of success in using this path. Conversely, architectural modelers are finding they can hand off high-level test-benches, including software-driven testbenches, to RTL verification teams thanks to progress in the UVM-SystemC standard. Food for thought – maybe you don’t think you’re ready yet but you might want to find why others have already started.

Tuesday late morning Harry Foster will present on trends in functional verification based on a double-blind survey in 2016. If you didn’t get a chance to see this his summaries last year though Mentor webinars, this is a chance to hear the whole thing in one go. This talk is worth the time for several reasons:

- You can see where your team sits relative to industry averages in adoption of major technologies

- You can see where you sit relative to others on power verification

- Most important (or embarrassing) of all, you can see where you sit relative to others in schedule overrun and reasons for respins

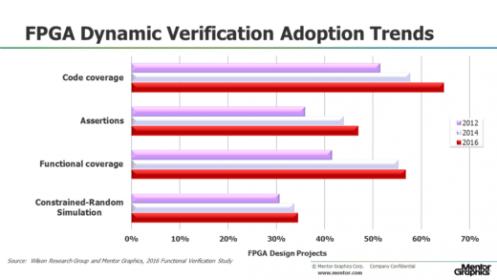

- You get to understand that FPGA verification has become just as complex as ASIC verification, using constrained random, coverage and even formal methodologies

On Wednesday, there’s a great panel in the early afternoon asking the hard question – looking back over 15 years, was SystemVerilog really the best answer to our verification needs? Phil Moorby (the guy who created Verilog and played a significant part in SystemVerilog) is on the panel along with participants from Mentor, Cadence, Synopsys and of course Cliff Cummings so this can’t fail to be fun. Panelists will also talk about what they think an ultimate replacement for SV might look like.

Mentor is all over Thursday. They kick off the morning with how to use just formal (no simulation) to verify a drone’s electronics so you can send the thing off with a message to come recuse you from a desert island. Perhaps you’d never go that far with formal, but pushing it to the limit is a good way to understand how to better use formal more broadly. For lunch Harry Foster and Steve Bailey from Mentor are going to discuss the need for a platform to support enterprise verification, looking at trend analyses across IPs and across designs to identify opportunities to reduce risk, spur innovation and introduce new methods.

And in the afternoon, they’re going to reprise a popular topic – how to build a complex testbench quickly when you’re not a UVM expert. While UVM has been widely adopted as the standard for developing testbenches, the fact remains that many engineers still struggle with the complexities of the language and often fail to use it as effectively as they could. Sure, they’ll get up the curve eventually but design schedules wait for no man or woman. There are ways to become more effective quickly without having to first become a UVM back-belt – this tutorial will show you how.

Now for papers. Rich Edelman, a friend from way back, kicks off Tuesday morning with a paper on using the  Direct Programming Interface. At the same time (darn), Mentor is presenting on a random directed approach to low power coverage, which sounds like an important one to hear. Wednesday mid-afternoon is a Mediatek/Mentor paper which should get an award for best title – “Ironic but effective; how formal analysis can perfect your simulation constraints”. And again, unfortunately at the same time there’s a paper on making legacy verification suites portable for the PSS standard.

Direct Programming Interface. At the same time (darn), Mentor is presenting on a random directed approach to low power coverage, which sounds like an important one to hear. Wednesday mid-afternoon is a Mediatek/Mentor paper which should get an award for best title – “Ironic but effective; how formal analysis can perfect your simulation constraints”. And again, unfortunately at the same time there’s a paper on making legacy verification suites portable for the PSS standard.

The posters are always well worth checking out. This year they include speeding up functional CDC verification, incrementally refining UPF to manage the complexity of power state tables and (especially interesting to me) using Jenkins continuous integration to improve regression efficiency. If you’re following state of the art methods in continuous build and delivery automation, you’ll know that Jenkins already plays a significant role in software development flow and is starting to make its way into some hardware flows. This poster could be a nice introduction to some of the techniques and benefits.

You can get full details HERE. Make sure you sign up for the conference!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.