When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things) devices gaining momentum, any sub-optimal solution for power is unwarranted. These devices operate at extremely low voltages and require minimum power consumption. Hence, it’s essential that the power measurement, analysis and optimization is accurate, consistent at all levels, and is well correlated with the power consumed by actual applications running on these devices.

Recently, I had talked about great innovations in power calculation, analysis and management at system level involving emulation technologies that allow capture of power numbers while live applications run on the system. I am happy to learn about yet another innovative and impressive power solution that is fast and accurate, and seamlessly works at all levels including system, RTL and gate with well correlated power numbers.

Cadencehas come up with an excellent power analysis solution with a large capacity that can run at the system-level as well as integrates with implementation level analysis. The Joules RTL Power Solution provides time-based RTL power analysis which can be accurate like gate-level implementation.

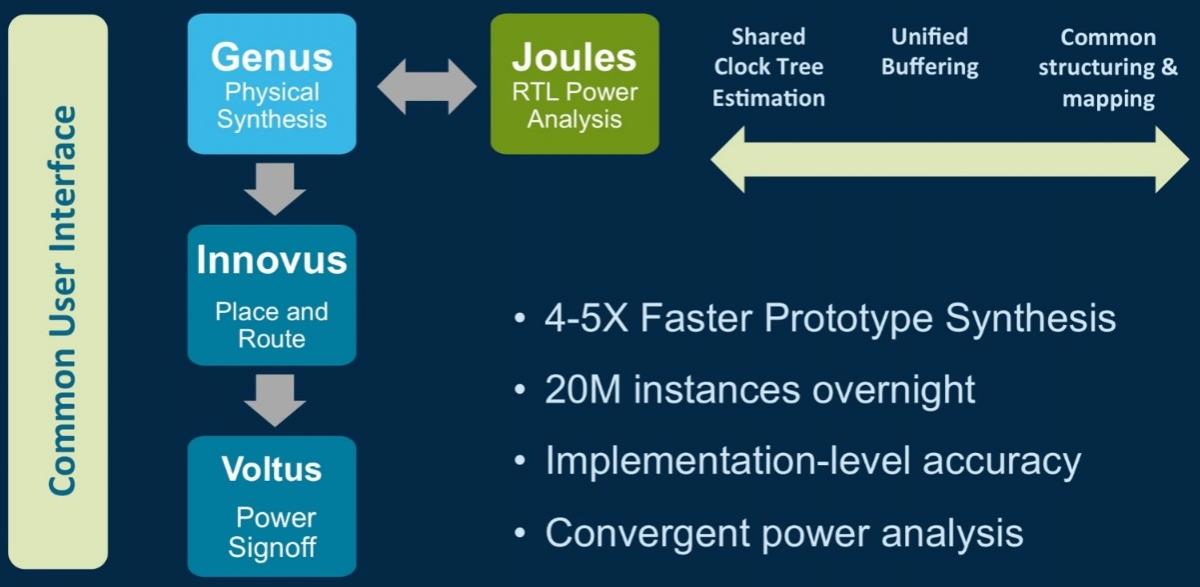

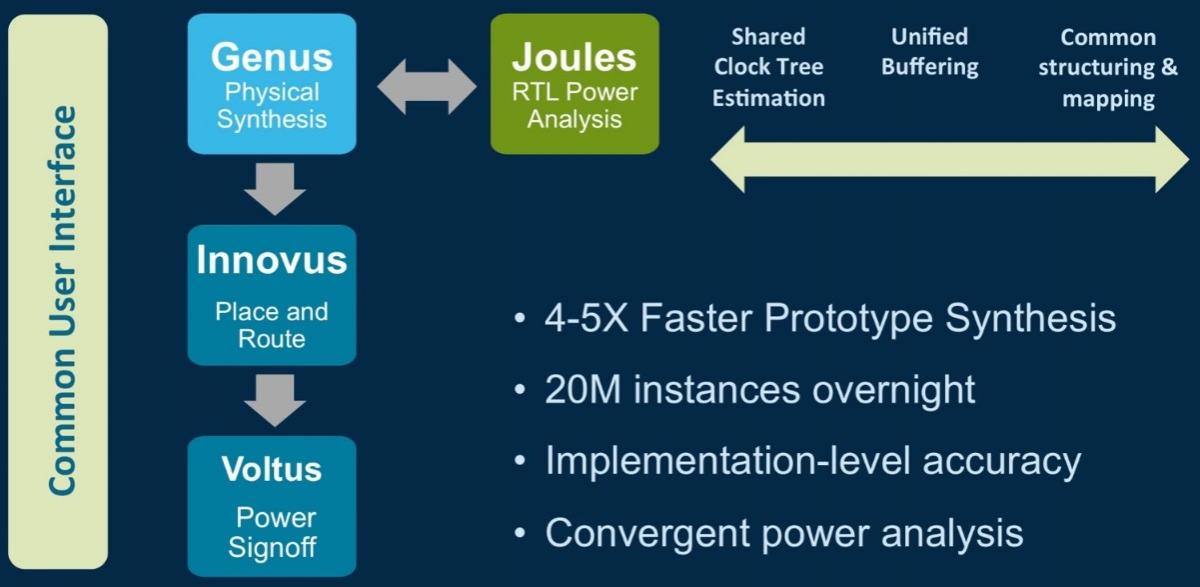

The Joules power analysis is seamlessly integrated with Cadence Genus Synthesis Solution. The Genus Synthesis utilizes a newly added rapid prototyping technology which provides order of magnitude faster design synthesis. The solution thus provides implementation-level accuracy in the power estimation.

The power analysis uses a multi-threaded architecture utilizing multiple CPUs that accelerates power exploration and enables an in-depth analysis. The solution allows simultaneous analysis of multiple stimulus files and each stimulus file can be time-sliced into frames to enable time-based power reporting. Also, multiple stimulus files across different design hierarchies can be merged to model full SoC traffic and identify peak power and clock gating opportunities. The power solution has a rich suite of library analysis and profiling tools for advanced analysis and debugging. The profiling of cells can be done by drive strength versus area, delay or power. The power reporting can be done in terms of bit or register level and can be categorized based on cell type, power type, design hierarchy, clock domain, power domain, or timing mode.

Also, there is a seamless integration between Cadence’s Joules RTL Power Solution, Palladium Emulation Platform and the Stratus HLS (High-Level Synthesis) Platform. For an early and accurate, time-based system-level power analysis and optimization, the Joules power analysis can be invoked directly from the Palladium Dynamic Power Analysis Solution GUI. The native read and write to/from Palladium database allows analysis of live software applications running on the hardware early in the development cycle. The peak and critical power frames in a long system-level simulation can be zoomed in for analysis with increased resolution and identification of correct time-slice for IR-drop. The Stratus HLS platform leverages Joules solution during high-level synthesis to provide SystemC level power profiling. The Stratus also enables IP teams to better evaluate system-level micro-architecture tradeoffs for power optimization.

This power analysis solution is quite fast at system-level while its result correlates well with that at the gate-level implementation and signoff.

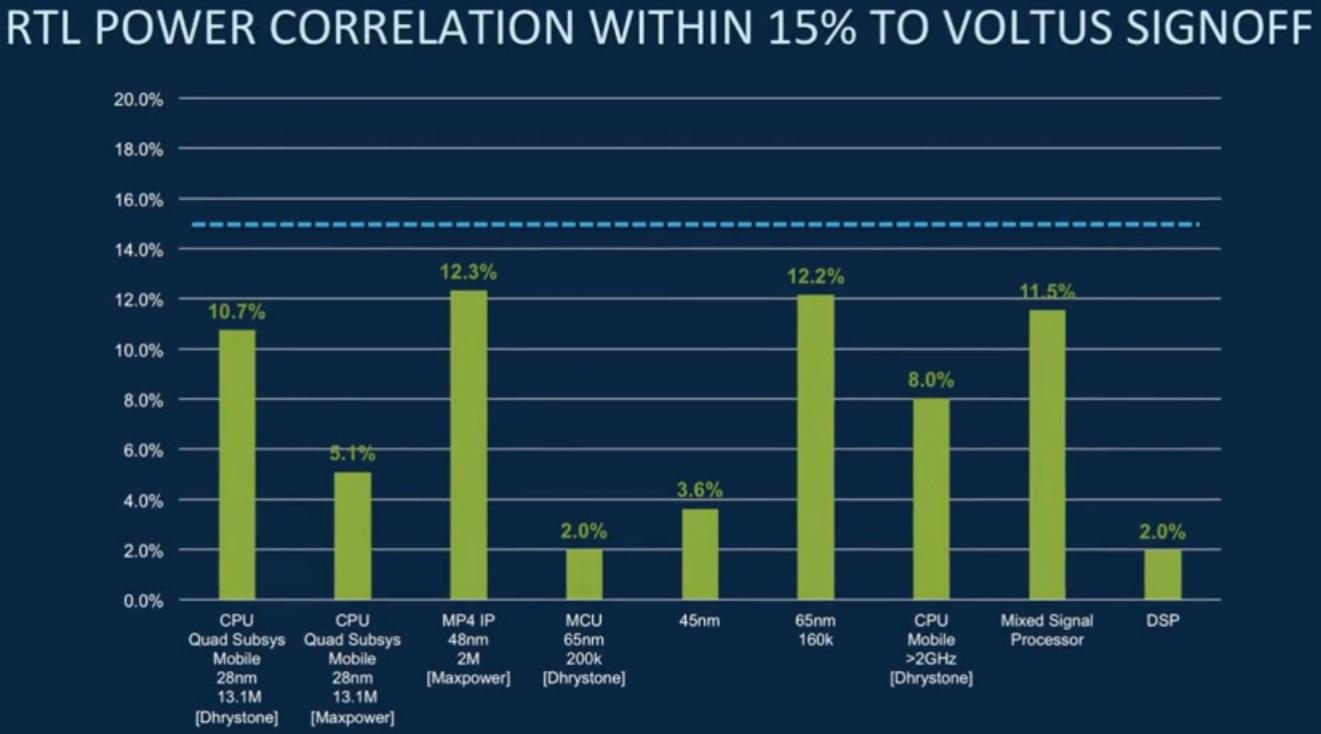

The Joules RTL power analysis was performed on several customer designs. The results were within 15% accuracy to signoff in the Cadence Voltus IC Power Integrity Solution with unified power calculation and advanced RTL-to-gate name mapping.

The Joules power solution provides about 20 times faster time-based power analysis compared to other methods. By using this solution with its integrated prototype synthesis, a design with 20 million instances can be analyzed overnight with gate-level accuracy within 15% of signoff in Voltus IC Power Integrity Solution.

Also read:

How Emulation Enables Complex Power Intent Modeling

Power Analysis Needs Shift in Methodology

How PowerArtist Interfaces with Emulators

Pawan Kumar Fangaria

Founder & President at www.fangarias.com

Comments

There are no comments yet.

You must register or log in to view/post comments.