There are three critical goals that designers of custom digital designs and memories look to achieve with high sigma verification:

(1) obtaining accurate results,

(2) achieving results with good run-time (efficiency), and

(3) gaining proper insight into how their circuit is behaving along with an understanding of failure modes that most affect high-sigma performance. Problems can then be identified and optimization tools can then be employed for tuning circuits to correct those problems.

A “black-box” approach taken by methods based on sampling and response surface models looks easy at first glance but falls short in all three categories: they introduce significant sampling errors, suffer from long runtimes, and provide little insight into the circuit’s different failure modes. In particular, there is no verifiability in black-box modeling methods. The user gets easily lulled into a sense of security by sample plots, but is not aware how unsafe these plots are as they show only a tiny fraction of data points chosen by a model. MunEDA tools offer to the designer added insight into their circuit behavior at extreme levels of variation rather than using a very limited “trust-us” approach.

MunEDA provides a fully-scriptable environment where each circuit preparation, analysis, optimization and reporting step can be programmed into a completely automatable flow (think Matlab and other industry-standard programming environments). MunEDA employs worst-case analysis (WCA) to rapidly locate the most-likely failure modes of your memory, clock-tree, analog, and mixed-signal circuits.

MunEDA WCA is based on the concept of most probable points (MPP), widely used for engineering reliability analysis and reliability-based design [1]. By virtue of their efficiency, accuracy, and providing insight into the analyzed problem, MPP-based methods are very popular for high-sigma verification tasks. WCA is an extension of MPP that simultaneously solves for worst-case corner and worst-case mismatch.

In [2], Intel engineers explain how MPP works and why it is their method of choice for verifying and optimizing yield, area, and power of register files and bitcells in microprocessors. A large number of different registers and bitcells is used in a CPU; for each one, high-sigma analysis is run many times, swept over process variants, corners, Vcc_min, etc. In [3], Intel engineers apply MPP method to carefully consider two failure modes of interest in their sequential logic circuit.

Due to the large number of required MC runs, efficiency of WCA is key. Typical runtimes of WCA-based 6 sigma analysis today are in the range of only 150 simulation runs compared to the requisite minimum 500 billion runs of standard MC to achieve the same accuracy.

Being able to run high-sigma efficiently is also important for designers who need to run it inside of an optimization loop. Due to mixed effects between operating conditions, corners, local variation, and device geometries, high-sigma analysis has to be executed multiple times during one optimization run.

One interesting property of embedding WCA into MunEDA’s environment is how analyzing different failure modes gives valuable insight into circuit behavior, which cannot be achieved using black-box sampling methods.

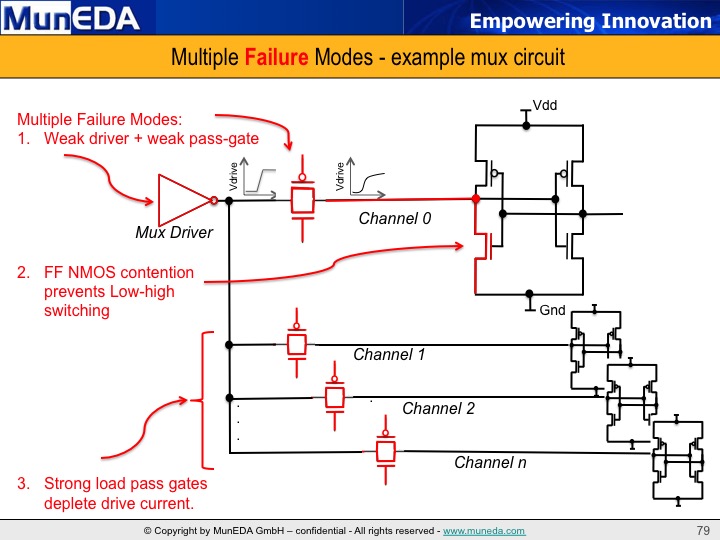

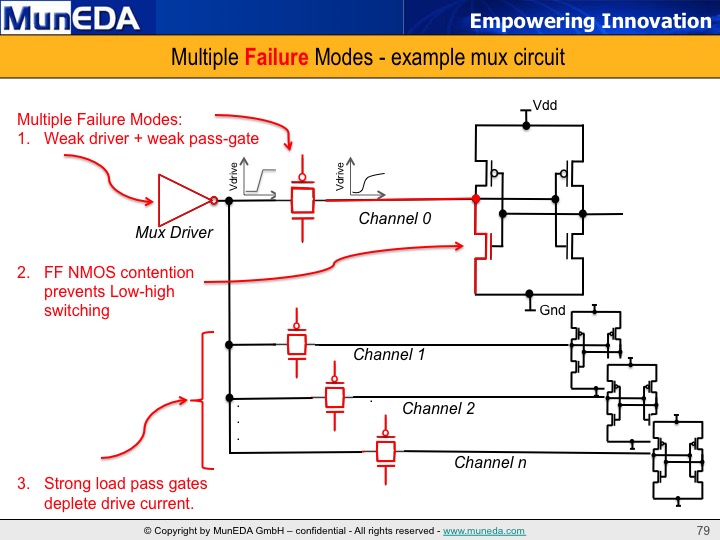

Take the example of the multiplexer circuit shown in Figure 1 above. As often happens with other types of circuits there are multiple failure modes of concern. Turning a black-box analysis tool loose on the circuit without providing input as to where to look will risk locating only one failure mode and maybe not the one of most critical interest. It’s especially problematic if a failure mode has a steep transition cliff, such as the nFET contention problem shown in figure 1.

Using MunEDA’s professional-grade environment for analyzing circuits with multiple failure modes, designers can consider all of their failure modes in succession and be sure not to miss one.

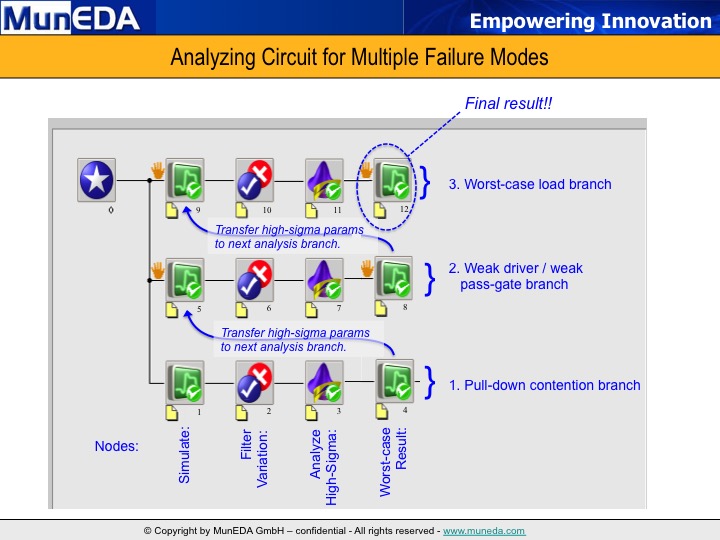

Figure 2 shows a run flow within the environment for analyzing multi-level failure modes in the arena of high-sigma analysis.

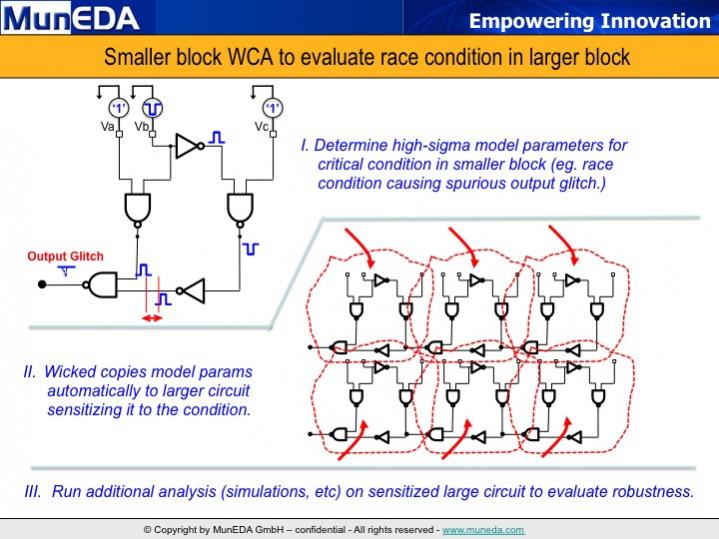

Another application for WCA is in evaluating timing and race conditions along delay paths in clock circuits and other timing circuits. This approach gives valuable insight into circuit behavior, which cannot be achieved using black-box sampling methods. MunEDA’s modular and fully-scriptable analysis canvas provides the ability to analyze and attain confidence in timing solutions. Consider the example shown in Figure 3, which shows a delay-path circuit.

To truly understand circuit behavior at high-sigma and ultra high-sigma it is necessary to use professional-quality tools that allow designers to really understand the circuit, tools that MunEDA provides. MunEDA tools for circuit migration, analysis, optimization and modelling have been proven in thousands of silicon tape outs with many of the top semiconductor companies worldwide. Please follow this link to see customers who are using MunEDA’s “WiCkeD” platform: https://muneda.com.

[1] X. Du et al.: “Most Probable Point-Based Methods.”

In : A. Singhee, R. A. Rutenbar (ed.): Extreme Statistics in Nanoscale Memory Design. Springer, 2010.

[2] K. Anshumali et al.: “Circuit and Process Innovations to Enable High-Performance and Power and Area Efficiency on the Nehalem and Westmere Family of Intel Processors”. Intel Technology Journal, vol.14 no.3, p.112-114.

http://www.intel.com/content/www/us/en/research/intel-technology-journal/2010-volume-14-issue-03-intel-technology-journal.html

[3] CH. Chen, K. Bowman, C. Augustine, Z. Zhang, J. Tschanz. “Minimum Supply Voltage for Sequential Logic Circuits in 22nm Technology”. IEEE Symposium on Low Power Electronics and Design. 2013, pp. 181-186.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.