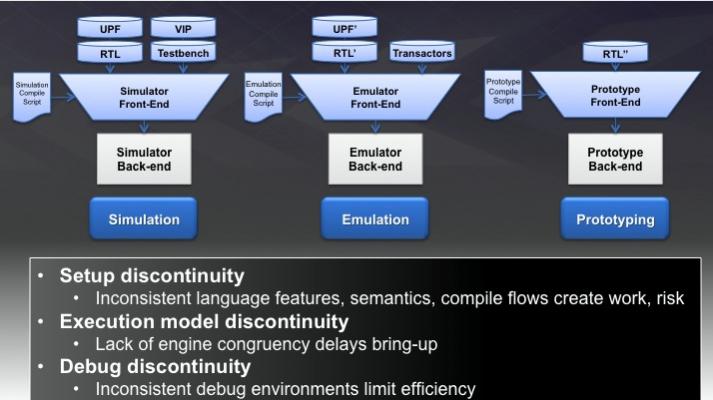

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required completely different scripts, changes to the RTL, and a lot of time, sometimes measured in months. Getting a large design up and running in emulation or an FPGA prototype system, in particular, was a major challenge.

Verification spans a number of different technologies, from virtual platforms, RTL simulation, formal techniques, emulation and FPGA prototyping. Going back a few years, most of these technologies came from separate companies and one effect of this was that moving the design from one verification environment to another required completely different scripts, changes to the RTL, and a lot of time, sometimes measured in months. Getting a large design up and running in emulation or an FPGA prototype system, in particular, was a major challenge.

Over the last couple of years, Synopsys has assembled a broad portfolio of leading edge technologies. They have rewritten their static and formal engines, acquired 3 virtual platform companies, acquired EVE’s emulation technology, and Springsoft’s Verdi debug environment. But these tools largely still showed their roots as separate product lines with different scripts and different requirements on inputs. It was still too hard to get a design that was running cleanly in, say, VCS into an emulator. It is important for verification to be able to move up and down the chain of engines easily, so that the best tool for the job can be used as the design proceeds through the development process.

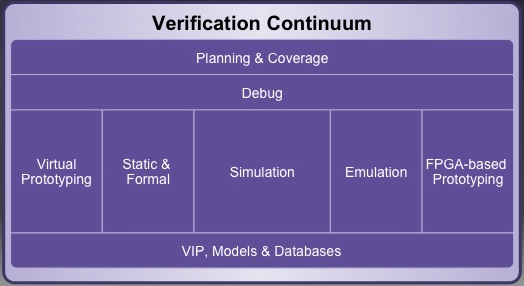

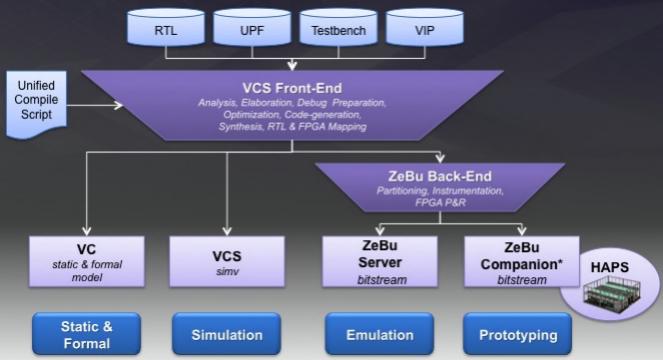

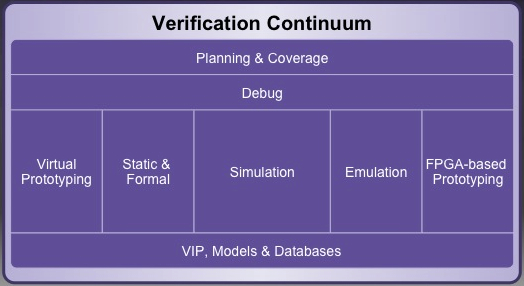

Earlier this week, Synopsys announced their Verification Continuum Platform. This is a major rewrite of the front ends of all of the various verification engines so that they have a common input, common scripts and so on. This gives seamless transitions between engines and a consistent interface for setup, runtime and debug. Earlier in the year, Synopsys announced Verification Compiler which pulled together formal and simulation into one environment. With this week’s announcement, that has now been broadened to pull in virtual platforms, emulation and FPGA prototyping too.

The VCS front-end is used for all compilation, analysis, elaboration, debug preparation, optimization, code-generation, synthesis and mapping. One immediate effect is that compile times for emulation are up to 3 times as fast as before.

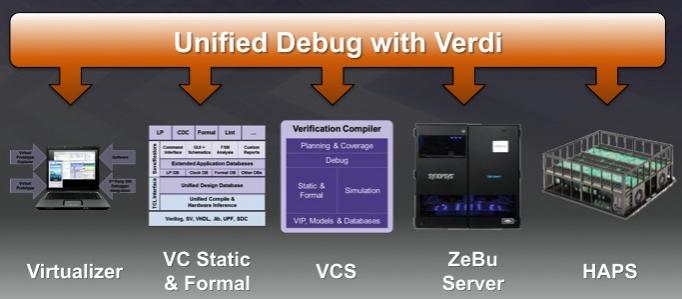

There is also unified debug with Verdi across all the technologies from virtualizer, through simulation, formal techniques, Zebu emulation and FPGA prototyping with HAPS.

The result is a “shift left” of the bug discovery process, enabling bugs to be found earlier and enabling software development to be done earlier. Obviously this has the potential to accelerate product development schedules significantly and, by making the technology easier to use, increase the use higher performance technologies such as emulation, FPGA prototyping and virtual prototyping.

More articles by Paul McLellan…

Comments

There are no comments yet.

You must register or log in to view/post comments.