The emerging market for IoT and wearable devices are designed with mixed-signal IP that includes: embedded CPU, flash, analogue and radio.EDA and IP companies have recently worked together to allow us to design an MCU with mixed-signal IP blocks more efficiently. This morning I attended a webinar with presenters from ARMand Cadence Design Systems. I’ve been following ARM more closely after they acquired IP provider Artisan back in 2004.

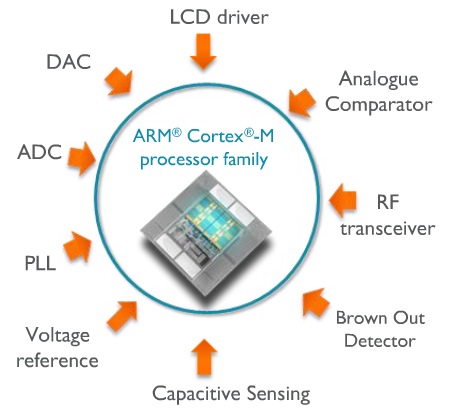

Diya Soubra from ARM started out the webinar and talked about “Smart Analogue”, digital circuits tuning analog functions for things like: Smart sensors, motor control and power management. The Internet of Things also requires analog sensors. Micro controllers (MCU) are taking on a lot more analog features.

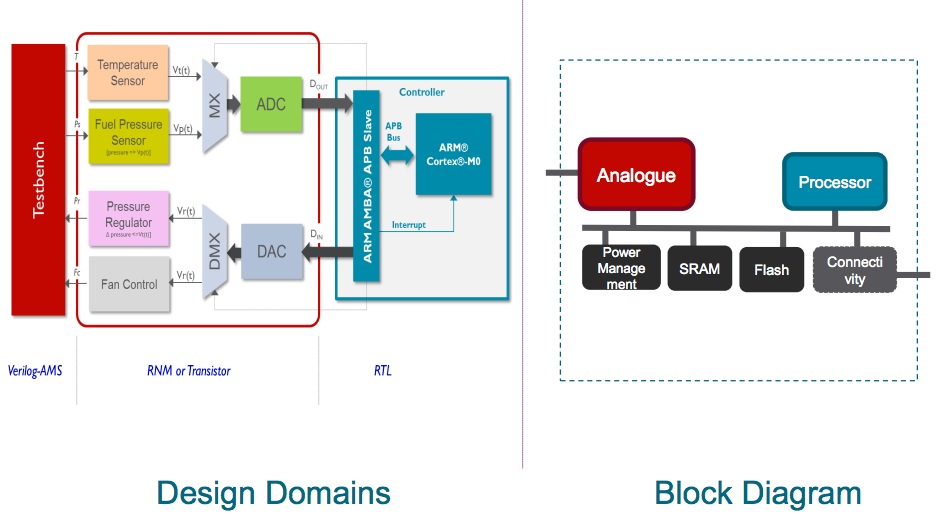

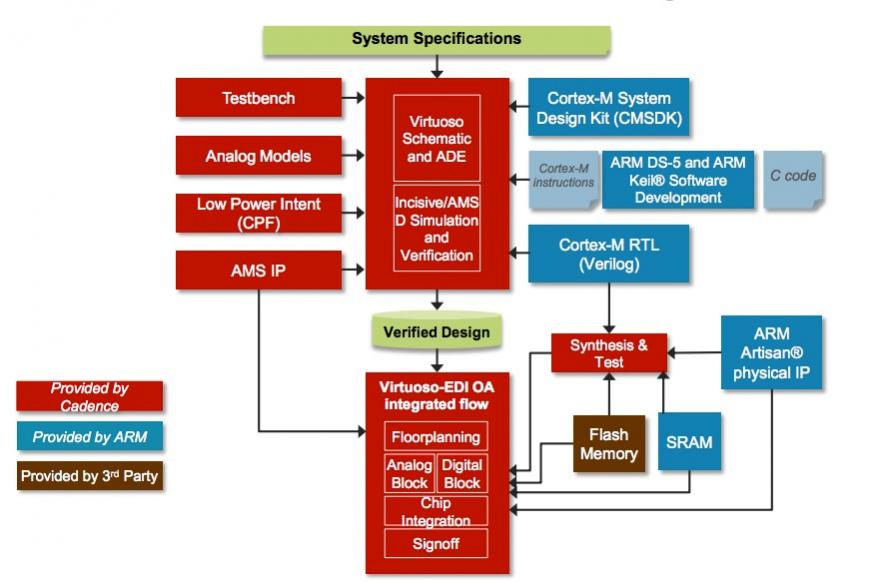

Mladen Nizic from Cadence shared how they have created a reference design flow with ARM for AMS design.

ARM has a Cortex-M system design kit that enables a Cadence tool flow for schematic capture, simulation and functional verification.

You can design either digital-centric with digital on top, and add analog blocks underneath. Another design flow is analog-centric where the top level is analog using schematics, and then any digital content is just an instance. For analog-centric design you can speed up simulation by creating an abstract model, instead of always simulating at the transistor-level with SPICE. Cadence provides about 200 templates for common analog building blocks that you can use to get started quickly with analog behavioral modeling. The use of Real Number Models enables fast analog simulation results. You can even swap out a Real Number Model with a transistor-level model for even higher accuracy, but at the cost of slower speed.

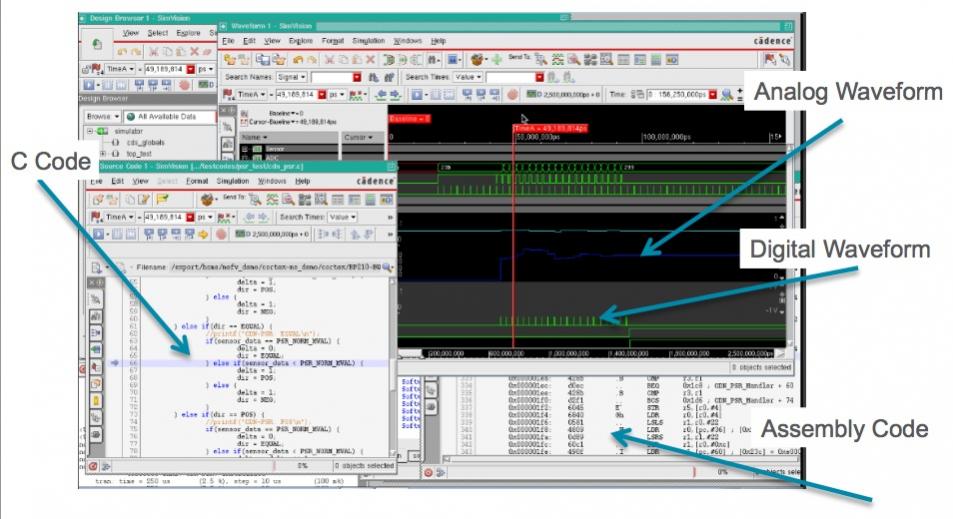

In this mixed-signal design flow you can actually debug your software and hardware running together.

Achieving a low-power design is challenging, so using the Common Power Format (CPF) enables simulation of multiple power domains for both digital and analog cells. Static verification techniques are also used to ensure correctness.

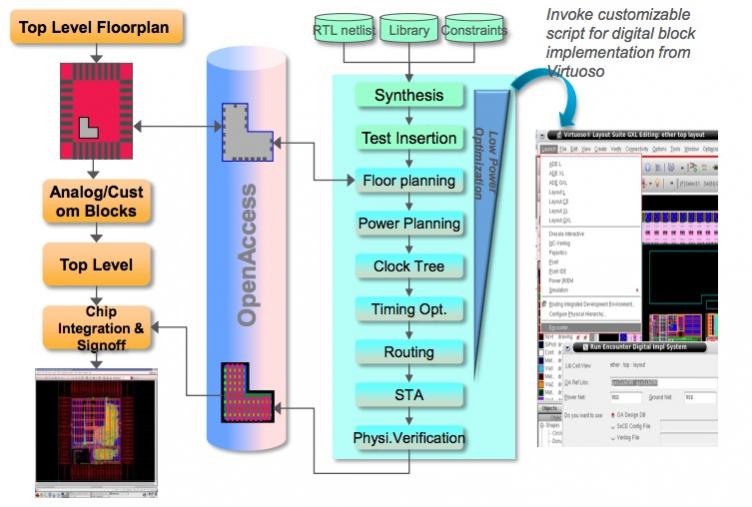

For physical IC implementation there is a Schematic Driven Layout (SDL) flow in Virtuoso for all of the analog pieces. On the digital side there’s an automated flow from RTL to placed cells. The flow for both analog and digital implementation is shown below:

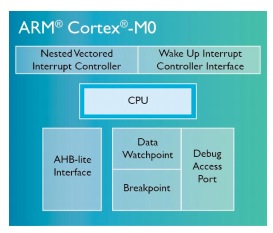

Diya Soubra from ARM detailed the mobile-optimized processor called Cortex-M0, which is a 32 bit processor for use in mixed-signal and IoT devices.

On a 180nm process node this M0 processor consumes only 73uW/MHz, and at 40nm it uses just 4uW/MHz. The processor reaches these low power numbers by using three major techniques: architectural clock gating, “Sleep-on-exit” interrupt handling and a wakeup interrupt controller.

ARM also provides a Cortex-M System Design Kit which includes:

- Plug processor in and start desgning

- Essential AMBA interconnects and peripherals

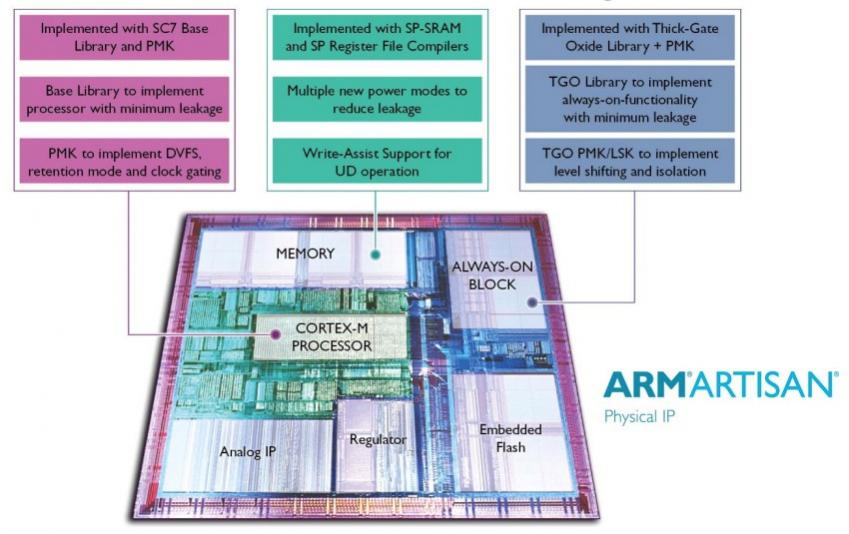

Joel Rosenberg from ARM showed the family of process nodes for ARM processors and which choices were best suited for embedded and IoT applications. ARM also provides physical IP needed to create an SoC:

For IoT you can often achieve low power and small area using a register file compiler instead of SRAM blocks. ARM Artisan memory blocks have four different modes for sleep levels so that you can trade off power versus wake-up times. A Power Management Kit (PMK) can also be used to manage a low power flow. You can do a free comparison of ARM IP by using an online form for a variety of foundries and nodes, generating an actual data sheet of results. See designstart.arm.com

Q: How does that C-compiler work with Virtuoso?

A: That C-compiler comes from ARM, then we simulate in Cadence

Q: What types of products are being designed with your AMS IP?

A: The main applications have been Motor controller, power conversion, power control.

Q: What does ARM offer for low power memory?

A: Our memory compilers are used in conjunction with flash memory, where programs are loaded from flash into SRAM for lowest power consumption.

Q: Tell me more about the latency in waking up IP blocks?

A: The M0 processor wakes up in about 10 cycles or more, depending on clock and PLL implementations.

Q: What kind of analog IP is available?

A: Cadence has acquired Cosmic and has convertors, sensors, etc. You can simulate with the abstracted real number models for fastest speed. ARM is focused on digital design blocks for IP.

Summary

You don’t have to start from scratch and cobble together your own AMS design flow with Cadence tools and ARM cores, instead consider starting off with their reference flow which includes the Cortex-M System Design Kit and ARM Artisan IP. That way you are spending valuable engineering time doing system design and getting to market more quickly. View the entire 60 minute webinar here.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.