Last year I was surprised at DAC by an un-heard of EDA company from China, ICScape. This year I followed up and spoke with Ravi Ravikumar about what’s new with ICScape in 2013.

Q: What’s new this year at ICScape?

We’ve released a product called PowerExplorer – leakage power optimization. Customers have done tape outs with it.

Q: Can you tell me about your EDA customers?

We do have new customers in the past year, tier 1, US-based, no comment on names.

Q: How many from ICScape at DAC?

At DAC – 15 people this year.

Full company 25 people.

Q: What other EDA tools do you offer?

We have analog tools that are OA-based.

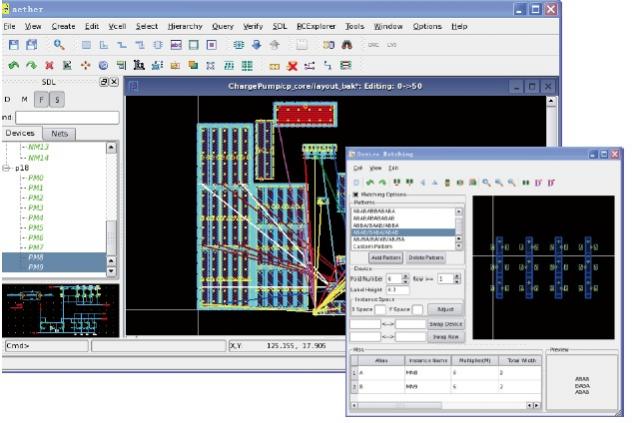

Schematic Driven Layout using Aether

Soc Timing ECO closure, and power reduction. It doesn’t matter what your tool flow is, if you have LEF/DEF then we can help your timing ECO closure.

Why? Cuts down to 2-4 iterations to reach closure. Not 10-12 iterations like with other approaches. Don’t touch the original placement. Our tools tell you that ther’s no legal placement for a cell to meet your timing.

Leakage Power – Give us a netlist, timing library, dont create timing violations. IC Explorer is the product family, makes sure not to create timing violations.

Requires STA data results.

AMS IC design tools – we have RC extraction and DRC/LVS tools as well. Pin 2 pin and point to point RC analysis interactively. You can wait until LVS clean to extract RC, or even earlier to get quick feedback.

Q: How are your tools sold around the world?

US – Contact HQ in Santa Clara, Johnson Lau & Jeff Havlaff.

Korea – Distributor.

Japan – Distributor.

Taiwan – Maojet.

China – HES.

Europe – Rep.

Q: Do your EDA tools support FinFET?

Yes, we are supporting AMS nodes for CMOS bulk, and developing support for FinFETs and FD-SOI.

Q: How is DAC for you this year?

DAC – much better results than expectations, booth has been full with meetings.

Q: How is business?

Tool evaluations – we’ve doubled our sales/AEs, so it makes evaluations go quicker.

Q: What trends do you see?

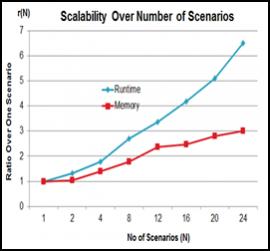

Too many SoC modes of operation (ie 200 modes), how can a P&R tool meet timing for all 200 modes? Built-in P&R engine that deals with timing engine that can concurrently converge on timing, eliminates impossible layout scenarios. Close the convergence loop.

Marvel – first customer success story.

lang: en_US

Share this post via:

Real men have fabs!