At DesignCon this week there was a panel on 3D standards organized by Si2. I also talked to Aveek Sarkar of Apache (a subsidiary of Ansys) who is one of the founding member companies of the Si2 Open3D Technical Advisory Board (TAB), along with Atrenta, Cadence, Fraunhofer Institute, Global Foundries, Intel, Invarian, Mentor, Qualcomm, R3Logic, ST and TI.

The 3D activities at Si2 are focused on creating open standards so that design flows and models can all inter-operate. In the panel session Riko Radojcic of Qualcomm made the good point that standards have to be timed just right. If they are too early, they attempt to solve a problem that either there is no consensus needs to be solved, or where the solutions are not yet known and thus cannot be standardized. If standardization is too late, then everyone has already been forced to come up with their own ways of doing things and nobody wants a standard unless it is simply to pick their solution. Riko reckons that 3D IC is about a year behind where he would like to see it and it risks the standards being too late and so everyone having to do their own thing. The Si2 open3D page is here.

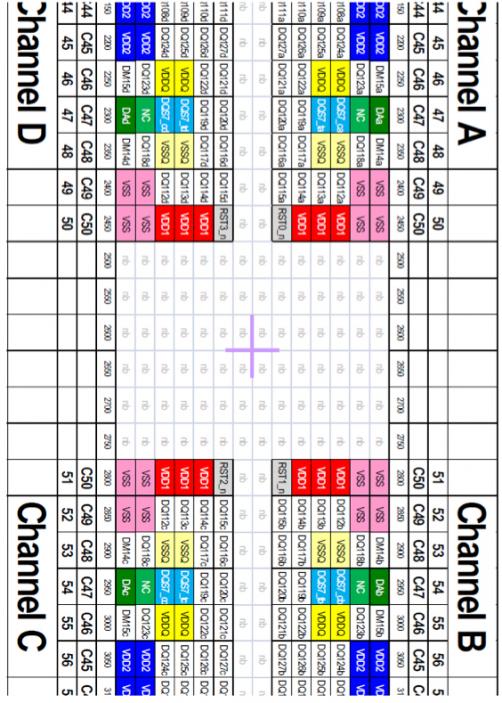

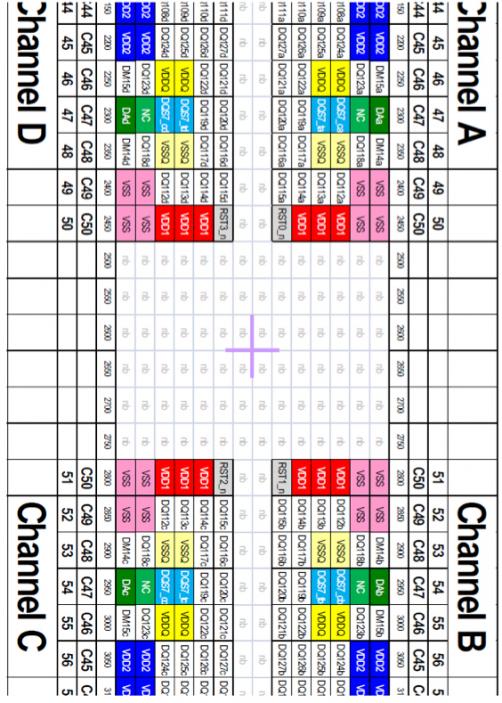

One standards that does now exist, as of earlier in January, is the JEDEC wide IO single data rate standard for memories. This includes the ball positioning and signal assigments that allows up to 4 DRAM chips to be stacked on an SoC and permits data rates up to 17Gb/s at significantly lower power than traditional interconnect technologies with 4 128b wide channels. The standard is here (free PDF, registration with JEDEC required). This should allow memory dice from different DRAM manufacturers to be used interchangeably in the same way as we have become accustomed to with packaged DRAM.

One standards that does now exist, as of earlier in January, is the JEDEC wide IO single data rate standard for memories. This includes the ball positioning and signal assigments that allows up to 4 DRAM chips to be stacked on an SoC and permits data rates up to 17Gb/s at significantly lower power than traditional interconnect technologies with 4 128b wide channels. The standard is here (free PDF, registration with JEDEC required). This should allow memory dice from different DRAM manufacturers to be used interchangeably in the same way as we have become accustomed to with packaged DRAM.

Apache is most interested in power delivery and thermal issues of course. Multiple tiers of silicon mean that the power nets on the upper tiers are further from the interposer and the package pins. In a conventional SoC, the IO power may make up 30-50% of all power and the clock another 30% or so. There is a lot of scope in 3D for power reduction due to the much shorter distances, the capability to have very wide buses. Nonetheless, microbumps and TSVs all have resistance and capacitance that affects the power delivery network and general signal integrity.

Thermal analysis is another big problem. Since reliability, especially metal migration, is affected by temperature severely (going from 100 degrees to 125 degrees reduces the margin by 1/3) the overall reliability can be very negatively affected if the temperature in the center of the die stack is higher than expected and modeled.

The big attraction of 3D is the capability to get high bandwidth at low power. It has the potential to deliver 1-2 orders of magnitude of power reduction on signalling versus alternative packaging approaches, as much as 1/2 Terabit/s between adjacent die.

Everyone’s focus in 3D standardization at the moment is to standardize the model interfaces so that details of TSVs, power profile of die, positioning of microbumps and everything can work cleanly in different tool and manufacturing flows. Note that there is no intention to standardize what the models describe (so, for example, no effort to standardize on a specific TSV implementation).

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.