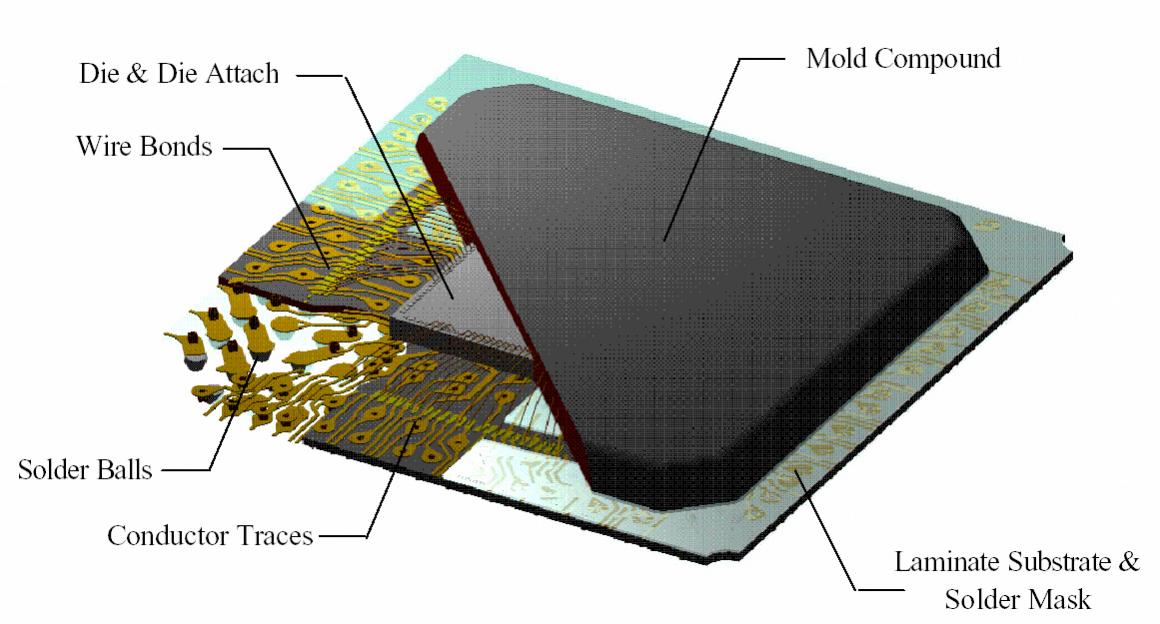

Chips, packages and circuit boards (systems, hence CPS) used to be three separate domains with their own tools that barely interacted at all. If you were lucky, reassigning a pin on a package wouldn’t have to be done manually in all 3 places. But now, from a signal integrity, noise, power point of view these three domains must be analyzed as a single system where everything interacts with everything else.

At DesignCon in February, Apache is running two workshops on these issues. Both are on Wednesday February 1st.

The first workshop, on CPS for Cost-down and Reliabilityis from 10.15 to 12.15. Apache along with featured speakers Dr Mondira Pant of Intel and Dr Amit Argawal of Cisco will share their insights and expertise in the area of chip-package-system (CPS) convergence and will discuss various aspects of analysis methodologies in terms of modeling, extraction and simulation. Topics will include comprehensive global power delivery optimization at the chip, package and board levels, system-level signal integrity analysis, along with case studies and real design examples.

The first workshop, on CPS for Cost-down and Reliabilityis from 10.15 to 12.15. Apache along with featured speakers Dr Mondira Pant of Intel and Dr Amit Argawal of Cisco will share their insights and expertise in the area of chip-package-system (CPS) convergence and will discuss various aspects of analysis methodologies in terms of modeling, extraction and simulation. Topics will include comprehensive global power delivery optimization at the chip, package and board levels, system-level signal integrity analysis, along with case studies and real design examples.

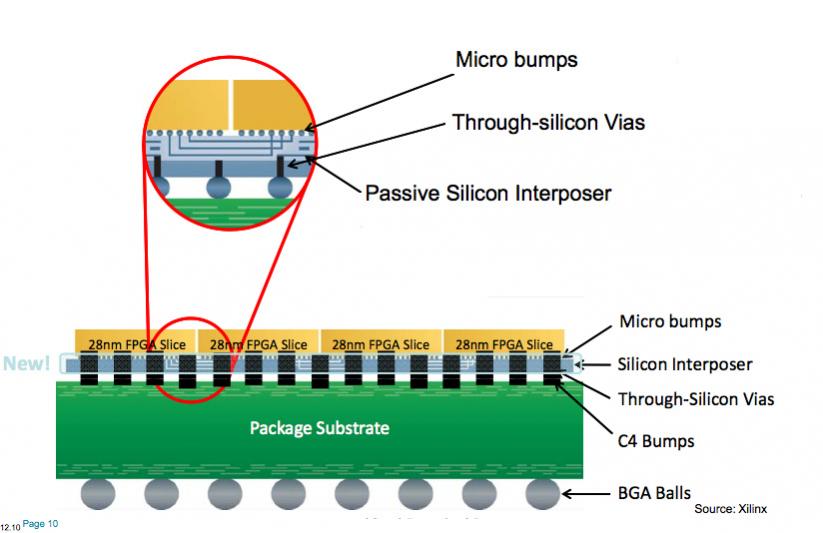

The second workshop, on CPS for 3D-IC and Power-Thermal-Mechanical-Electrical Applications is from 2-4pm. 3D stacked die and 2.5D Silicon Interposer chip designs with through-silicon vias (TSVs) have emerged as upcoming technologies, enabling designers to meet the performance, power, and form factor demands of today’s ICs. However, 3D-IC designers face unique challenges such as thermal-induced EM and reliability issues, along with place and route congestion due to TSV insertion. Apache and featured speakers Dr Tim Hollis of Micron, Ivor Barber from LSI and Dr Simon Burke of Xilinx will examine the various modeling and simulation challenges in 3D-IC design. Methodologies for the analysis of power delivery network, chip-to-chip communication, and thermal integrity will be covered using real case studies on designs.

The second workshop, on CPS for 3D-IC and Power-Thermal-Mechanical-Electrical Applications is from 2-4pm. 3D stacked die and 2.5D Silicon Interposer chip designs with through-silicon vias (TSVs) have emerged as upcoming technologies, enabling designers to meet the performance, power, and form factor demands of today’s ICs. However, 3D-IC designers face unique challenges such as thermal-induced EM and reliability issues, along with place and route congestion due to TSV insertion. Apache and featured speakers Dr Tim Hollis of Micron, Ivor Barber from LSI and Dr Simon Burke of Xilinx will examine the various modeling and simulation challenges in 3D-IC design. Methodologies for the analysis of power delivery network, chip-to-chip communication, and thermal integrity will be covered using real case studies on designs.

More details here including how to get 20% off your DesignCon conference pass or get a free exhibit pass (Apache is at booth 214).

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.