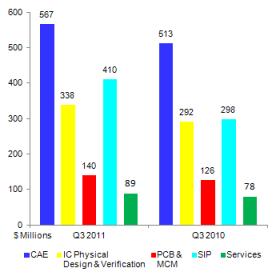

Thanks to Paul, who has shared EDAC resultsfor Q3 2011, we can see that Silicon IP has definitely passed CAE revenue! It does not appears clearly ($410 million for IP, 566.7 for CAE), but when you consider that ARM, among many other IP vendors, is not part of EDAC, it’s easy to see that SIP revenue is higher than CAE (ARM revenue for 2010 were $632 million; just add $158 million to $410 and you are done).

In fact, the important figure in this report is the 37.4% yearly growth rate.

That reminds me the presentation made during IP-SoC 2010, by a respected analyst firm, showing a forecasted growth for Design IP (or SIP, it’s the same) in the years 2011 to 2014 as follow:

- +6% in 2011,

- then +2.3% in 2012,

- +6.7% in 2013

- and 6.9% in 2014

My reaction was to post this blogin Semiwiki as I knew that this figures were far too low. When I say “I knew”, I mean some common sense had driven me to think about all the factors pushing for a higher growth rate. Let’s see the parameters:

- Microprocessor IPis 90% royalty based; the more SoC in production, the higher the revenue. Smartphone shipments are rocketing (40% growth rate in 2010, then 2011) and uP IP, dominant in mobile phone, is also penetrating the embedded world (Set-Top-Box, HDD, SSD, DVD…). Expected growth rate in this IP segment only is probably 15% CAGR for 2011-2015; at least!

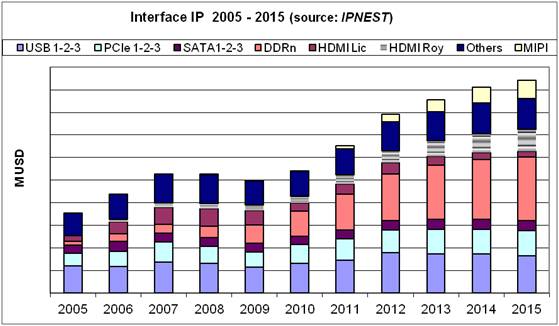

- Interface IP(USB, HDMI, MIPI, DDRn…) will pass from $250 million in 2010 to $450 million in 2014; that’s a 13% CAGR.

- Now, if we look at market trends, less tangible, we see that more ASIC/ASSP design starts are System on Chip (SoC), calling for more interfaces with the rest of the system (USB, PCIe, SATA, MIPI…), with memory (DDRn Controller) and more functions to be integrated, with, at best, the same number of engineers. The “make vs buy” question is quickly answered: there is not enough resource to design the numerous functions.

- Another trend is for a chip maker to concentrate on internally developing the real differentiating IP functions, not the standard based interfaces functions or the memories.

- And to develop a SoC with an even more aggressive Time To Market(TTM) requirement. Once again, the answer is frequently an externally sourced Design IP.

- To be honest, I should mention one point: the design start count is decreasing by 2 to 3 % every year. Paradox? Apparently, but if you dig, you realize that a higher proportion of design start is a SoC, and every design is integrating more functions…

So, you think: “one analyst has been wrong, that is not a casus belli!” I totally disagree! That’s a big deal! Why? Just have a look at what could be a virtuous circle:

Analyst Forecast of a certain market –> Financial decision makers identify this market to be fast growing –> Funding are easier to find to develop a company addressing a fast growing market

You will agree that, if analyst are making a 600% error (6% forecasted for actual being 37.4%) the virtuous circle is biased, and even more, is becoming a vicious circle! When analyst do not identify a high growth market, the decision makers, or VC, will not inject money at a place where they should do it. As an example, take the fabless market: since everybody (at least the MBAed) is talking about $50 million to invest to develop a SoC, which is true, but only true for 40nm or below, the fabless can’t get VC attention. But, there are numerous chips (mixed-signal, PMIC, niche ASSP and so on) which could be developed using 130nm or 90nm, at a few $ million cost, and could generate decent profit. Because an analyst brain is small (by definition), the guy will automatically associate Fabless with $50-100 million development cost, and pass! I am severe, as you have a better chance to find a more cleaver analyst when the company is built around people who have a real industry experience before joining! Like ABI research, for example (I am too modest to name IPNEST).

By the way, we had another example of this vicious circle last week-end: France and other European countries have lost their AAArank, after USA last summer. Thanks to analysts, the same guys who have assigned AAA to junk bonds in 2007, leading to the crisis in 2008-2009 and leading later the central bank in USA, to loan $1,200 billion at 0.01% to the banks, to save them from bankruptcy (the same has also occurred in Europe). The degradation of the AAA has been the way analyst and bankers have thanked the federal state (USA) or the state (France) for their loan. I tell you, analyst is the best job to do (if you plan to destroy the realeconomy)!

From Eric Esteve– IPNEST(Market analysis and Consulting – IP focus)

Share this post via:

The Data Crisis is Unfolding – Are We Ready?