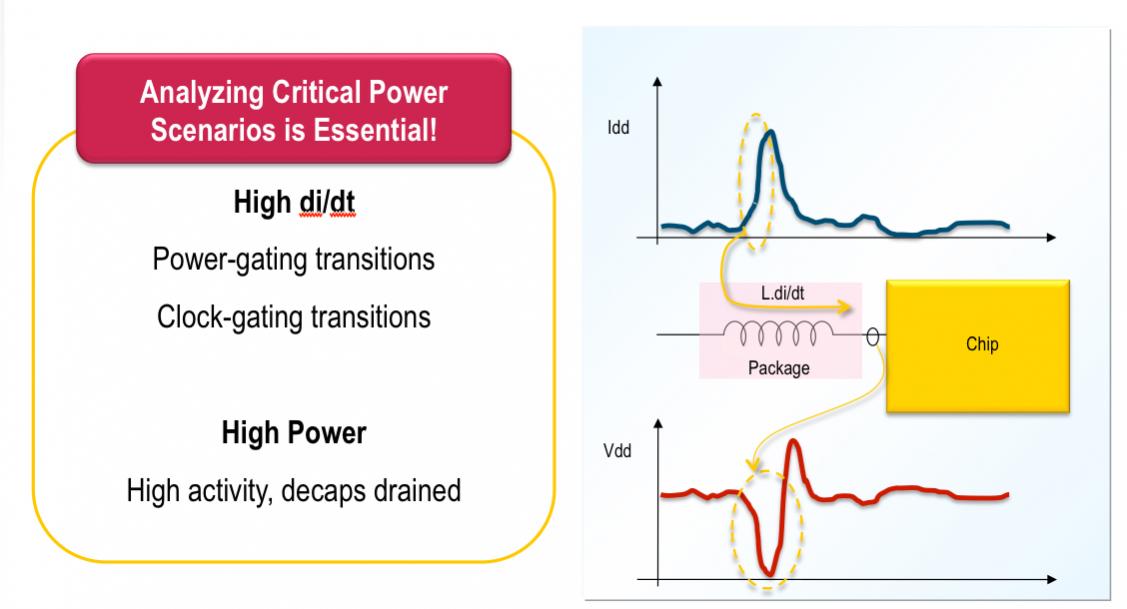

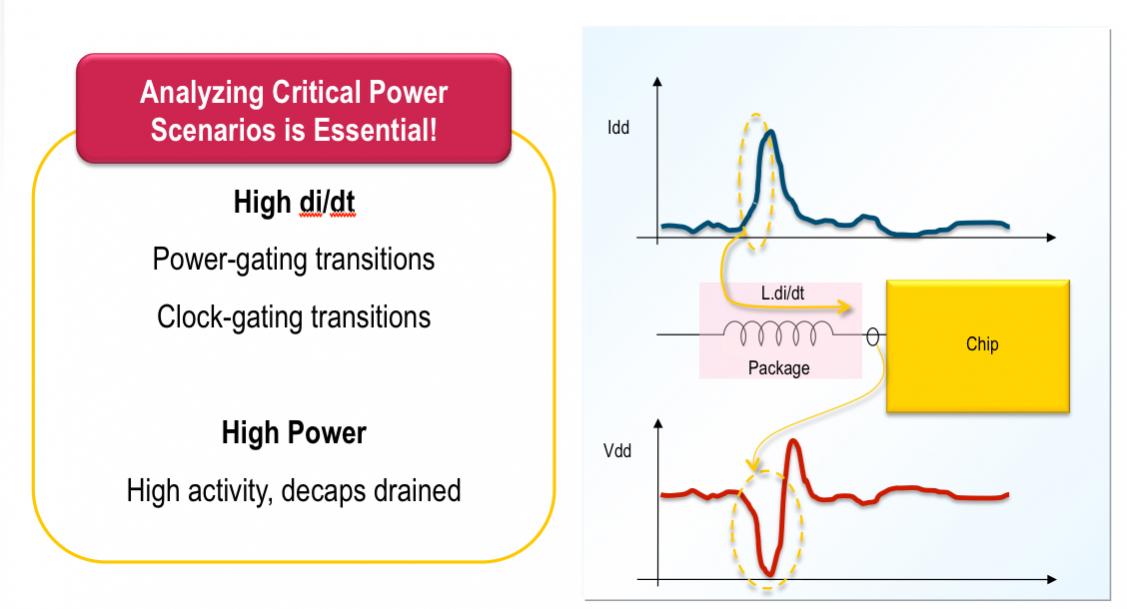

One of the challenges of doing a design in the 28nm world is that everything depends on everything else. But some decisions need to be made early with imperfect information. But the better the information we have, the better those early decisions will be. One area of particular importance is selecting a package, designing a power network and generally putting together a power policy. Everything is power sensitive these days, not just mobile applications but anything that is going to end up inside a cloud computing server farm, such as routers, disk drives and servers. Power gating and clock gating make things worse, since they can cause very abrupt transitions as inrush current powers up a sleeping block or a large block suddenly starts to be clocked again.

But these decisions about power can’t wait until physical design is complete. That is too late. And the old way of handing things with a combination of guesswork and excel spreadsheets is too cumbersome and inaccurate. The penalties are severe. Underdesigning the power delivery network results in failures; overdesigning it results in larger die or a more expensive package. The ideal approach would be to be able to do the sort of analysis that is possible after physical design, but instead do it at the RTL level.

But these decisions about power can’t wait until physical design is complete. That is too late. And the old way of handing things with a combination of guesswork and excel spreadsheets is too cumbersome and inaccurate. The penalties are severe. Underdesigning the power delivery network results in failures; overdesigning it results in larger die or a more expensive package. The ideal approach would be to be able to do the sort of analysis that is possible after physical design, but instead do it at the RTL level.

That is basically what Apache is announcing today. An RTL power model (RPM) of the chip combines three technologies.

- Fast critical frame selection

- PACE (Power Artist Calibrator and Estimator)

- RTL (pre-synthesis) power analysis

To do power analysis requires vectors (well, there are some vectorless approaches but they are not very accurate). But all vectors are not created equal. There might be tens of millions of vectors in the full verification suite, but for critical power analysis there may be just very short sequences of a dozen vectors that cause the maximum stress to the power network or which cause the maximum change in the current. These critical frames are the ones that are needed to ensure that there are no power problems due to excessive current draw or excessively fast change that, for example, drains all the decaps.

PACE, PowerArtist Calibrator and Estimator, is a tool for analyzing a chip for a similar application and process and generating the parameters that are required to make the RTL power analysis accurate for similar designs. Obviously power depends on things like the capacitance of interconnect, the cell library used, the type of clock tree and so on. PACE characterizes this physical information allowing RTL-power based design decisions to be made with confidence.

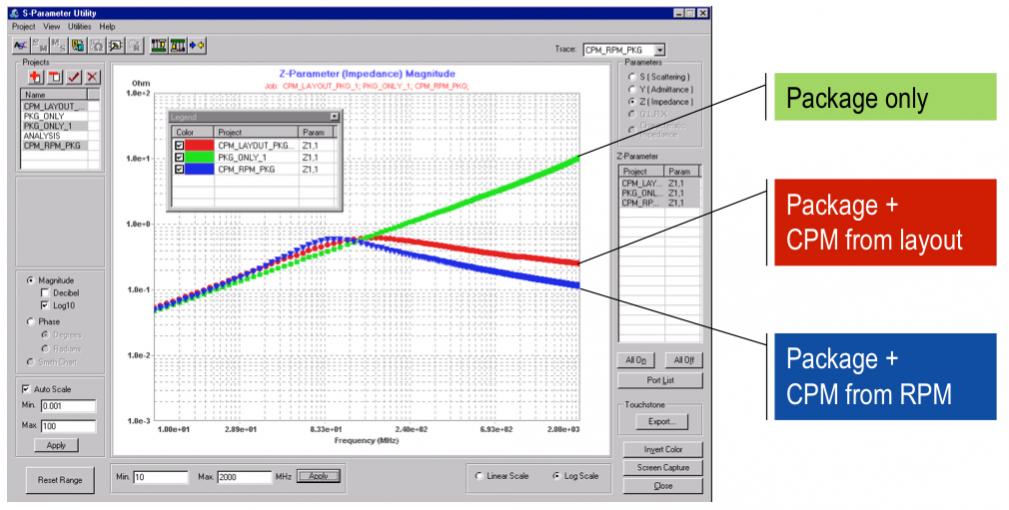

With these two things in place, the critical frames and the data in PACE, plus, of course, the RTL, it is now possible to generate an RTL Power Model for the design. The RPM can then be used in Apache’s analysis tools. How accurate is it? Early customers have found that the RPM is within 15% of the values from actual layout with full parasitics. For example, here is a comparison of package resonance frequency comparing just the package (green) with the package along with a CPM (chip-power-model) from layout (red) and with the package along with a CPM from RPM (blue).

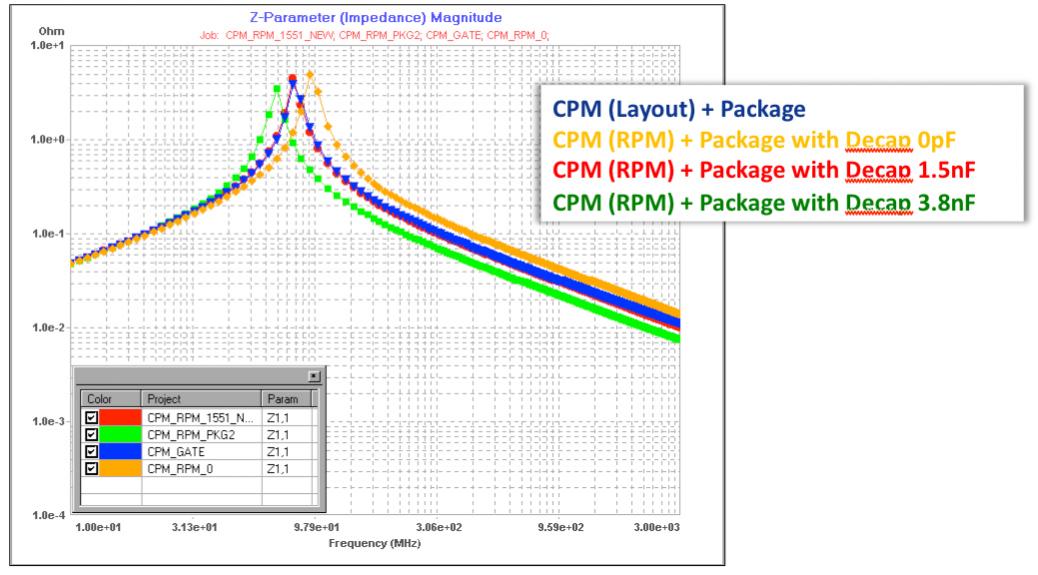

And another example, showing the change in resonance frequency as the size of the decoupling capacitors is changed.

More and more designs are basically assemblies of IP blocks, mostly RTL. The RTL is often poorly understood since it is purchased externally or created in another group overseas or comes from a previous incarnation of the design. This makes early analysis like this even more important and avoids either underdesigning the power delivery network, and risking in-field failures, or overdesigning it and being uncompetitive due to cost.

Share this post via:

Comments

0 Replies to “RTL Power Models”

You must register or log in to view/post comments.