Synopsys made a pretty major announcement regarding their new ASIL-B,C and D ready embedded vision processor IP. This matters because you cannot bolt on the design elements and features needed to achieve these ASIL levels later, and this IP is absolutely necessary for ADAS systems and other critical safety systems in automobiles. These features have to be baked into the architecture, and the tools necessary to support them also need to be available. Simultaneously, Synopsys has gone to great lengths to ensure that the added safety features have minimal impact on performance.

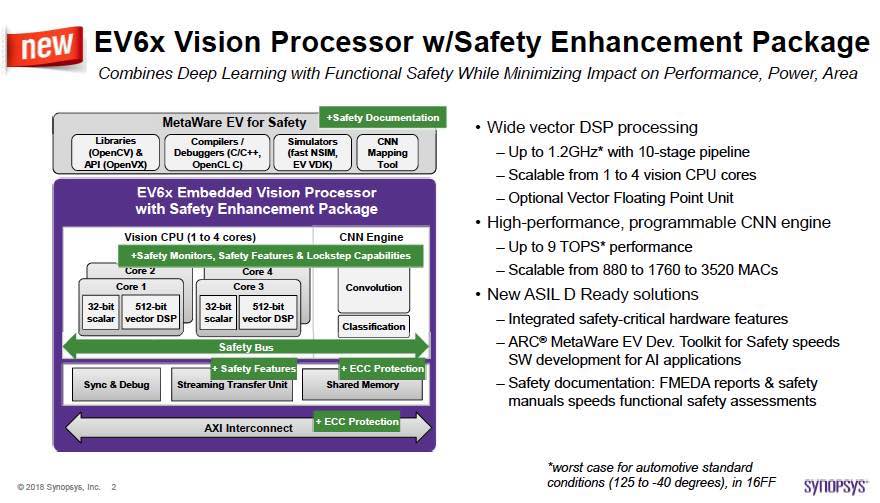

So, what exactly are some of these features? Their press release itemizes them: “lockstep capabilities, ECC memories, error checking on core registers and safety-critical registers, a dedicated safety monitor, and a windowed watchdog timer for each core. An optional dedicated safety island monitors and executes safety escalations and diagnostics within the SoC and protects system bring-up”.

However, a list of safety features is not enough, there are a few more essential elements needed to crack the barrier to successfully implementing a vision processor based SOC for a system that complies with ISO 26262. Performance and capability are the first two major items to check off. The other necessary piece is development tools that are also ASIL ready. Let’s talk about these in order. I was fortunate enough to chat with Gordon Cooper, Product Marketing Manager at Synopsys for EV processors, about these topics. Much of what he discussed went beyond the press release and made it easier to understand their latest announcement.

Gordon told me that the crux of the announcement is that they have added the Safety Enhancement Package to their EV6x family of vision processors. Also, they have added vector processing that runs up to 1.2GHz with a 10 stage pipeline. The 1.2GHz speed, he pointed out, is at worst case for automotive standard conditions of 125 to -40 C in 16FF. Performance like this is much harder to achieve in these conditions, however they represent what is commonly found in automotive operating environments. Gordon emphasized that benchmarking for these applications is extremely important, it’s not enough to read a spec sheet and try to make a decision.

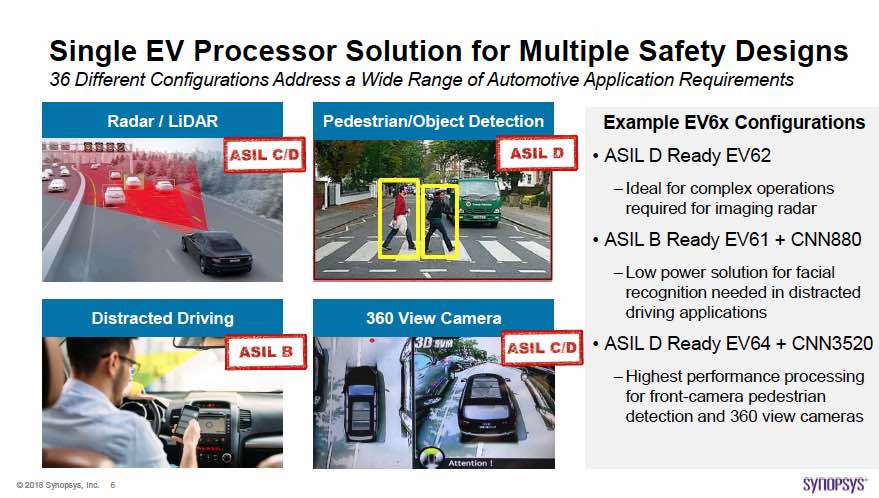

Gordon talked about data processing requirements for these systems as well. They are seeing 3-4 megapixel image sizes at frame rates of 30 fps, and increasing. By 2020 there will be over 24 cameras per vehicle as well as radar, all with higher resolutions. Yet, for different tasks, there needs to be differentiation in the kind of processor that is required. For instance, monitoring a driver’s face to detect distracted driving is a far different task than pedestrian or object detection. Synopsys offers different configurations of its EV6x family for each of these categories of tasks.

Gordon says that after thorough examination they have decided that 8 or 12 bit precision is preferred to the 16 bit precision often used. TensorFlow coefficients start out as 32 bit float, but they are quantized to 12 or 8 bits for recognition applications, with 8 bit being suitable in most instances.

On the tools side, they have invested in creating the documentation necessary to facilitate ASIL-D qualification. The tool chain has EV runtime and libraries, including OpenVX and OpenCV kernel libraries. They support C/C++ and OpenCL for developing applications and vision kernels. In addition, there is comprehensive debugging tool support. Synopsys also has a CNN graph mapping tool that helps mapping to the CNN engine. System level simulation support is available with system level models for host and EV processors.

Synopsys already has a large presence in the automotive market. Their processors are used in almost every application within that space. They already have customers who have taken some of the ASIL-D ready EV6x family to silicon. Availability of this IP will help accelerate ISO 26262 certification. Gordon also made it clear that they are going to be supplying their customers with a steady stream of updates to ensure they benefit from the latest research in vision processing. There is extensive material available on their website about the EV6x vision processor family and the Safety Enhancement Package that provides ASIL-D readiness.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.