In the wake of increased global competitiveness and shorter time-to-market windows, there has been a renewed focus by design management on the underlying data management infrastructure of the design teams. An increasing number of systems-on-chip (SoCs) now have some type of analog, digital and/or RF modules, making it imperative for analog, RF and digital designers to collaborate well on designs and to share design data easily across multiple design sites. This year, it is predicted that more than 121 billion analog integrated circuits (ICs) (Ref: Semico Research) will be used in all electronic devices, a substantial analog content in the SoCs being shipped. And with RF components also slowly beginning to make inroads into SoCs, the development lines between analog, digital and RF designs are slowly but surely starting to get blurred.

Given the challenges of managing large design teams with different technical abilities and located across different locations, design management in a number of semiconductor companies have begun to realize the necessity and benefits of providing a common data management solution capable of handling all types of designs: analog, RF, digital and mixed-signal. Some of the most important criteria that design teams look for while evaluating SoC design data management software are:

- Performance and fault tolerance

- Security

- Robustness

- Disk usage

- Ease of use

- Project management

In this article, we will discuss one of the criteria for selecting data management software, namely performance and fault tolerance.

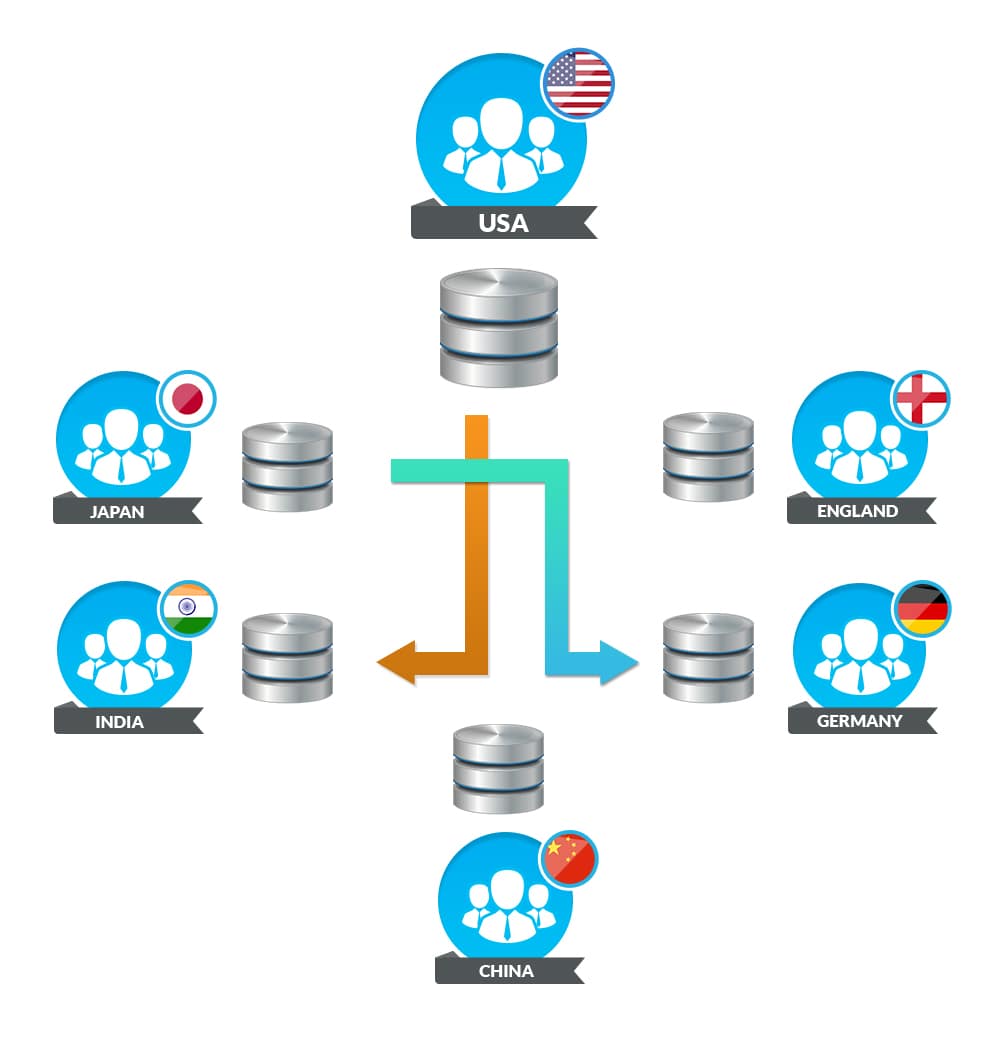

Most semiconductor design companies, including startups, are nowadays inclined to have remote design centers at different locations, such as India, China, Vietnam, Korea, etc. To ensure efficient 24×7 productivity for the designers, the performance of a design data management solution becomes a key criterion. Performance depends on a number of factors, such as network speed and disk access times, the architecture of the design data repository and the manner in which design data is transferred, use of caches at design sites, how the user workspaces are updated, multi-streaming, etc.. Hardware and network considerations aside, let us review some of the other factors that impact performance, beginning with the selection of the type of design repository.

There are two main types of design data repositories, Centralized and Distributed:

The centralized repository is historically the oldest type of design data repository and is widely deployed by a number of software data management solutions. One of the main advantages of the central repository is that it easy to set up and typically works well when the entire design team is based in a single location. On the flip side, in a centralized design repository, there is only one database for all design projects, and tasks such as browsing the revision history of a file, creating a tag, and comparing different versions of a design object are limited by the speed of the network connection.Unfortunately, the centralized repository model does not fit well in today’s SoC design environment, as most semiconductor design companies, including small startups, have remote design centers and the sizes of the design projects are relatively large. If the project is large or there are a large number of projects hosted at that site, there will be an increase in WAN traffic, which leads to the sluggish and sub-optimal performance at remote sites. Data management operations that need to contact the primary server — such as check-in/out, tags, browsing and comparing version history — get affected most due to the WAN link acting as a bottleneck.

A centralized repository also becomes a liability for design companies by having a single point of failure. Any problems with the network hosting the design repository or any loss in the connectivity between the primary and remote site can have severe implications. All the members of the entire design team, located at multiple locations worldwide, are unable to access the design data. The delays can have an adverse effect on the design schedule as well.

A distributed design data repository, on the other hand, is more flexible and provides better fault tolerance. It allows for the design data to be partitioned so that design centers can have their own localized design repositories. This ensures that design teams at remote sites benefit in performance, since the design data is stored at the same location as the user and is typically on a high-speed and reliable network.It is very common practice while designing SoCs to use existing design projects (IPs), some of which may not be hosted on the same design site as the user. The distributed repository architecture provides designers with the flexibility to reference projects from other design sites and get updates as needed. Designers working locally get notified whenever any changes are made to the reference projects, regardless of their location, and can choose when to update the IP version. An additional benefit of using a distributed repository is that there is no single point of failure. A failure on the network connectivity for a design site has minimal impact on the rest of the design team at other locations, as they use their own local repositories.

One must note that the concept of distributed repositories in the semiconductor industry is slightly different from that in the software world. Software data management systems such as Git replicate the repository of files onto each user’s workarea, making it an independent revision control repository without being connected to the central repository. Users of software data management systems can create their own revisions and eventually or timely merge them into the main repository as needed and reconcile the changes, if any. For software or text files, this approach works well, but when it comes to merging large binary files, as is the case with SoC designs, reconciling the design modifications can often be a challenge.

For most remote design sites, the bottleneck has been the time it takes to update a work area and obtain all the changes made at the other sites. A number of files, perhaps hundreds, varying in size, might have been changed since the user last updated the work area and must be brought across the WAN. This can have a big impact on the productivity of users at remote design sites. To resolve this problem, it becomes necessary to have a cache server that caches the latest versions of all the files used at that design site. With the presence of a cache, users would be getting the latest versions of the files from the local cache across the LAN instead of the WAN. This approach greatly reduces WAN bandwidth usage and dramatically improves performance.

The manner in which a user’s workspace is managed by the data management system will also have an impact on performance. A user’s workspace can typically have a large number of files, of different types and varying sizes. In a typical design development environment, each user has a workarea with a physical copy of a revision of each file. In such cases, it can take a considerable amount of time to update the work area with the latest version of the files from either the local cache or across the WAN.

A links-to-cache mechanism, on the other hand, provides better performance when workareas are created using files that are symbolic links to a cache managed by a cache server. The cache server maintains a copy of revisions of files being used by all the workareas at a design site. A physical file is copied over to the workspace only when the user intends to edit the file. The symbolic links are updated only when the user decides to update the workspace. Creating a symbolic link into the cache is a much faster operation compared to physically copying the latest version of the files, some of which may be quite large in size. In the links-to-cache model, a physical copy of only the files that need to be edited are maintained and copied over. This model provides users with a stable workarea over which they have full control (even when symbolic links are being used), faster performance and optimizized disk space by using links to shared revisions. Additionally backups and management of the workarea are much faster because of the symbolic links.

In addition to selecting the correct type of repository, it is also important to ensure that the design data management software makes full use of available bandwidth. The notion of multi-streaming data (not to be confused with multi-threading) ensures that there is no latency between the various operations required for data transfer, once it starts, and the network bandwidth is optimally used.

Design teams will continue to grow and spread across multiple locations. The file sizes will also continue to grow by leaps and bounds. With such constraints, it is natural to continue to leverage the advancements made in data network speeds and protocols as well as to develop better mechanisms to improve the performance. With tight design schedules, most designers would like the ability to have the latest version of design data at their fingertips. At ClioSoft, we are committed to make that happen.

About ClioSoft

ClioSoft, Inc. is the pioneer in the field of SoC design configuration management and enterprise IP management solutions for the semiconductor industry. Built exclusively for hardware design engineers, with flexibility to adapt to complex flows, ease of use and robustness as the main drivers, ClioSoft’s SOS Design Collaboration Platform empowers design teams located at multiple sites to collaborate efficiently on complex RF, analog, digital and mixed-signal designs. Using SOS, design teams can streamline the development of complex SoC designs from design specification to tapeout by efficiently sharing and managing their design data across different design centers using a distributed, fault-tolerant architecture. To handle the requirements of complex SoC design flows, the SOS platform is integrated with major EDA flows — Cadence’s Virtuoso® technology, Keysight Technologies’ Advanced Design System (ADS), Mentor Graphic’s Pyxis Custom IC Design, Synopsys’ Galaxy Custom Designer® and Laker3™ Custom Design.

The sole objective of ClioSoft’s collaborative IP management solution is to improve design reuse within a company. ClioSoft helps semiconductor companies catalog and manage internal and third-party IPs, providing an easy-to-use administration and user cockpit to manage the process of creating IPs and their derivatives, their lineage, IP licensing, security, and issue and defect tracking.

Also Read

The Case for Data Management Amid the Rise of IP in SoCs

ClioSoft SOS v7.0: Faster, Smarter and Stronger

Starvision and SOS, a Perfect Match

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.