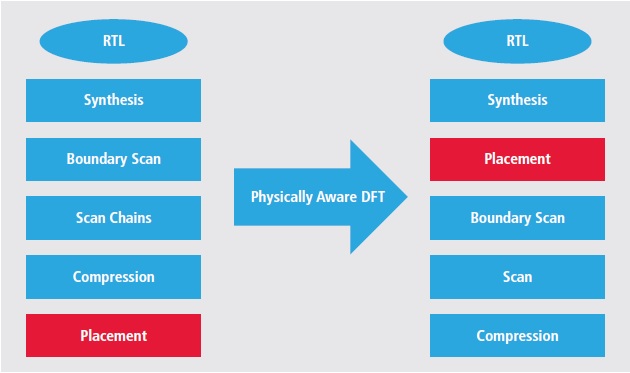

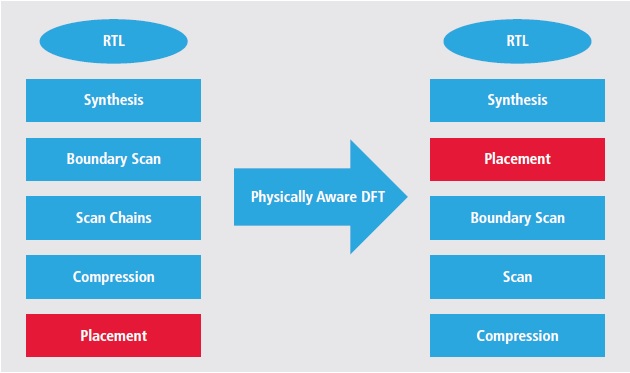

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan flip-flops’ that contain logic targeted for improving testability. Scan chains are formed by connecting scan flip-flops serially that allow Automatic Test Pattern Generation (ATPG) tools to control and observe the sequential state of the design and to generate test patterns to achieve the highest fault coverage. Further, extra circuitry can be added to compress test data volume and optimize test time. Also, several self-testing logics, such as logic built-in self-test (LBIST) and memory built-in self-test (MBIST) can be added on a chip.Clearly, the DFT circuits are a must for testability, reliability and robustness of designs. However, they introduce overheads in terms of area and wiring which can increase power consumption and decrease performance of a design substantially. Also, accommodating clock domain crossing (CDC), clock-edge mixing, and voltage domain crossing in an SoC (which can have multiple modes of operations) needs extra hardware such as lock-up latch and voltage level shifter. This extra hardware introduces additional wiring along the scan path resulting into excessive wiring congestion. So, what’s the alternative in such a dilemmatic situation? We truly do not have a choice. We need to use the DFT circuitry. What if we have the best of both worlds? Here is a smart methodology where the overall design is optimized for best PPA (Power, Performance and Area). The idea revolves around doing design placement before test circuit insertion. Traditionally, placement is the last stage in the design flow when scan chain re-ordering is done to shorten long wires in the scan-paths. Naturally, this approach is limited in the sense that placement cannot be changed to a large extent. The break-point logic on the scan-path that involves lock-up latches, clock crossings, etc. cannot be affected to re-order flip-flops. Hence only feasible long wires can be re-routed. In a new approach at Cadence, a scan-mapped netlist is placed just after synthesis, before inserting DFT. Then, based on the placement, scan flip-flops are assigned to scan chains. Further, scan chain re-ordering is done as a final step.Cadence implemented this new methodology on a real wireless communication chip by using its ‘Encounter Digital Implementation System’ and ‘Encounter RTL Compiler Advanced Physical’ that provided an impressive gain of ~16% in scan-chain wire length reduction compared to traditional methodology. The net result in PPA optimization was ~42% saving in total negative slack in timing, ~5% saving in power and ~2% saving in area. Actual detailed data and the detailed steps applied in the flow by using these tools can be found in a whitepaperfreely available at Cadence website.The whitepaper also describes about how Encounter RTL Compiler leverages I/O pad placement information to optimally order the boundary-scan cells in the boundary-scan shift register. IEEE 1149.1 boundary-scan testing is essential for board-level interconnect testing. Here, boundary-scan cells are inserted between I/O pads and the system logic. The boundary-scan cells are serially connected and provide controllability and observability to board-level interconnects. Their ordering is also important to minimize long crossovers along functional paths.The Cadence’s physically aware DFT methodology is proven to prevent wiring congestion due to DFT insertions, thus providing significant improvements in power, performance and area optimizations of a design.

The idea revolves around doing design placement before test circuit insertion. Traditionally, placement is the last stage in the design flow when scan chain re-ordering is done to shorten long wires in the scan-paths. Naturally, this approach is limited in the sense that placement cannot be changed to a large extent. The break-point logic on the scan-path that involves lock-up latches, clock crossings, etc. cannot be affected to re-order flip-flops. Hence only feasible long wires can be re-routed. In a new approach at Cadence, a scan-mapped netlist is placed just after synthesis, before inserting DFT. Then, based on the placement, scan flip-flops are assigned to scan chains. Further, scan chain re-ordering is done as a final step.Cadence implemented this new methodology on a real wireless communication chip by using its ‘Encounter Digital Implementation System’ and ‘Encounter RTL Compiler Advanced Physical’ that provided an impressive gain of ~16% in scan-chain wire length reduction compared to traditional methodology. The net result in PPA optimization was ~42% saving in total negative slack in timing, ~5% saving in power and ~2% saving in area. Actual detailed data and the detailed steps applied in the flow by using these tools can be found in a whitepaperfreely available at Cadence website.The whitepaper also describes about how Encounter RTL Compiler leverages I/O pad placement information to optimally order the boundary-scan cells in the boundary-scan shift register. IEEE 1149.1 boundary-scan testing is essential for board-level interconnect testing. Here, boundary-scan cells are inserted between I/O pads and the system logic. The boundary-scan cells are serially connected and provide controllability and observability to board-level interconnects. Their ordering is also important to minimize long crossovers along functional paths.The Cadence’s physically aware DFT methodology is proven to prevent wiring congestion due to DFT insertions, thus providing significant improvements in power, performance and area optimizations of a design.

Sponsor

Podcast EP16: Hyperscale Computing & Changes in the Datacenter

Podcast EP90: A Tour of Cadence’s Cloud Solutions with Mahesh Turaga

Podcast EP105: Cadence STA Strategy and Capabilities, Today and Tomorrow with Brandon Bautz

Podcast EP112: How Cadence is Revolutionizing Full-Chip Signoff with Certus

Most Viewed Blog 2018

Most Viewed Blog 2017

Most Viewed Blog 2016

Most Viewed Blog 2015

Most Viewed Blog 2014

Most Viewed Blog 2013

Most Viewed Blog 2012

Most Viewed Blog 2011

Instance

Array

(

[node_name] => Cadence

[node_id] => Array

(

[0] => 2

)

)

Nodes

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[356] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[populated:protected] => 1

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[19992] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 49

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19992

[node_id] => 356

[title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[reply_count] => 0

[view_count] => 374

[user_id] => 25277

[username] => AmandaK

[post_date] => 1712619486

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 69112

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1712619486

[last_post_id] => 69112

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19865] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 50

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19865

[node_id] => 356

[title] => Revolutionary Cadence Reality Digital Twin Platform to Transform Data Center Design for the AI Era

[reply_count] => 0

[view_count] => 829

[user_id] => 25277

[username] => AmandaK

[post_date] => 1710889164

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 68499

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1710889164

[last_post_id] => 68499

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19864] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 51

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19864

[node_id] => 356

[title] => Cadence and NVIDIA Unveil Groundbreaking Generative AI and Accelerated Compute-Driven Innovations

[reply_count] => 0

[view_count] => 304

[user_id] => 25277

[username] => AmandaK

[post_date] => 1710889098

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 68498

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1710889098

[last_post_id] => 68498

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19833] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 52

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19833

[node_id] => 356

[title] => Cadence Collaborates with Arm to Jumpstart the Automotive Chiplet Ecosystem

[reply_count] => 0

[view_count] => 475

[user_id] => 25277

[username] => AmandaK

[post_date] => 1710447622

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 68407

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1710447622

[last_post_id] => 68407

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19767] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 53

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19767

[node_id] => 356

[title] => Cadence to Acquire BETA CAE, Expanding into Structural Analysis

[reply_count] => 0

[view_count] => 717

[user_id] => 25277

[username] => AmandaK

[post_date] => 1709673735

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 68178

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1709673735

[last_post_id] => 68178

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19730] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19730

[node_id] => 356

[title] => Cadence Expands Tensilica Vision Family with Radar Accelerator and New DSPs Optimized for Automotive Applications

[reply_count] => 0

[view_count] => 554

[user_id] => 25277

[username] => AmandaK

[post_date] => 1709332627

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 68050

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1709332627

[last_post_id] => 68050

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19668] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19668

[node_id] => 356

[title] => Cadence Digital and Custom/Analog Flows Certified for Latest Intel 18A Process Technology

[reply_count] => 0

[view_count] => 775

[user_id] => 25277

[username] => AmandaK

[post_date] => 1708553456

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67715

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1708553456

[last_post_id] => 67715

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19666] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19666

[node_id] => 356

[title] => Cadence and Intel Foundry Collaborate to Enable Heterogeneous Integration with EMIB Packaging Technology

[reply_count] => 0

[view_count] => 496

[user_id] => 25277

[username] => AmandaK

[post_date] => 1708553176

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67713

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1708553176

[last_post_id] => 67713

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19652] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19652

[node_id] => 356

[title] => Intel and Cadence Expand Partnership to Enable Best-in-Class SoC Design on Intel’s Advanced Processes

[reply_count] => 0

[view_count] => 532

[user_id] => 25277

[username] => AmandaK

[post_date] => 1708475784

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67682

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1708475784

[last_post_id] => 67682

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19607] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19607

[node_id] => 356

[title] => Cadence and Dassault Systèmes Unveil the First Cloud-Enabled, Collaborative Experience to Transform the Development of Electromechanical Systems

[reply_count] => 0

[view_count] => 795

[user_id] => 25277

[username] => AmandaK

[post_date] => 1707782189

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67485

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1707782189

[last_post_id] => 67485

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19556] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 59

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19556

[node_id] => 356

[title] => Cadence Unveils Millennium Platform—Industry’s First Accelerated Digital Twin Delivering Unprecedented Performance and Energy Efficiency

[reply_count] => 0

[view_count] => 845

[user_id] => 25277

[username] => AmandaK

[post_date] => 1707176383

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67216

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1707176383

[last_post_id] => 67216

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19536] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 60

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19536

[node_id] => 356

[title] => Cadence Significantly Advances ECAD/MCAD Convergence for Electronic Systems with New Celsius Studio AI Thermal Platform

[reply_count] => 0

[view_count] => 719

[user_id] => 25277

[username] => AmandaK

[post_date] => 1706740052

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67089

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1706740052

[last_post_id] => 67089

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19520] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19520

[node_id] => 356

[title] => Phison Deploys Cadence Cerebrus AI-Driven Chip Optimization to Accelerate Product Development

[reply_count] => 0

[view_count] => 696

[user_id] => 25277

[username] => AmandaK

[post_date] => 1706573503

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 67043

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1706573503

[last_post_id] => 67043

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19477] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19477

[node_id] => 356

[title] => Cadence Unveils New Palladium Z2 Apps with Industry’s First 4-State Emulation and Mixed-Signal Modeling to Accelerate SoC Verification

[reply_count] => 0

[view_count] => 729

[user_id] => 25277

[username] => AmandaK

[post_date] => 1705965360

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 66832

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1705965360

[last_post_id] => 66832

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[discussion_count] => 268

[message_count] => 269

[last_post_id] => 69112

[last_post_date] => 1712619486

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[last_thread_id] => 19992

[last_thread_title] => Cadence Named by Fortune and Great Place to Work as One of 2024’s 100 Best Companies to Work For, Ranking No. 9

[last_thread_prefix_id] => 0

[moderate_threads] => 1

[moderate_replies] => 1

[allow_posting] => 1

[count_messages] => 1

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 48

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 356

[title] => Cadence

[description] =>

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 355

[display_order] => 80

[display_in_list] => 1

[lft] => 51

[rgt] => 52

[depth] => 2

[style_id] => 0

[effective_style_id] => 4

[breadcrumb_data] => {"385":{"node_id":385,"title":"Companies","depth":0,"lft":13,"node_name":null,"node_type_id":"LinkForum","display_in_list":true},"355":{"node_id":355,"title":"Company Forums","depth":1,"lft":14,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[19448] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 63

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 19448

[node_id] => 356

[title] => GUC Tapes Out Complex 3D Stacked Die Design on Advanced FinFET Node Using Cadence Integrity 3D-IC Platform

[reply_count] => 0

[view_count] => 773

[user_id] => 25277

[username] => AmandaK

[post_date] => 1705368564

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 66678

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1705368564

[last_post_id] => 66678

[last_post_user_id] => 25277

[last_post_username] => AmandaK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[type_data] => []

)

[_relations:protected] => Array

(

[Forum] => XF\Entity\Forum Object

(