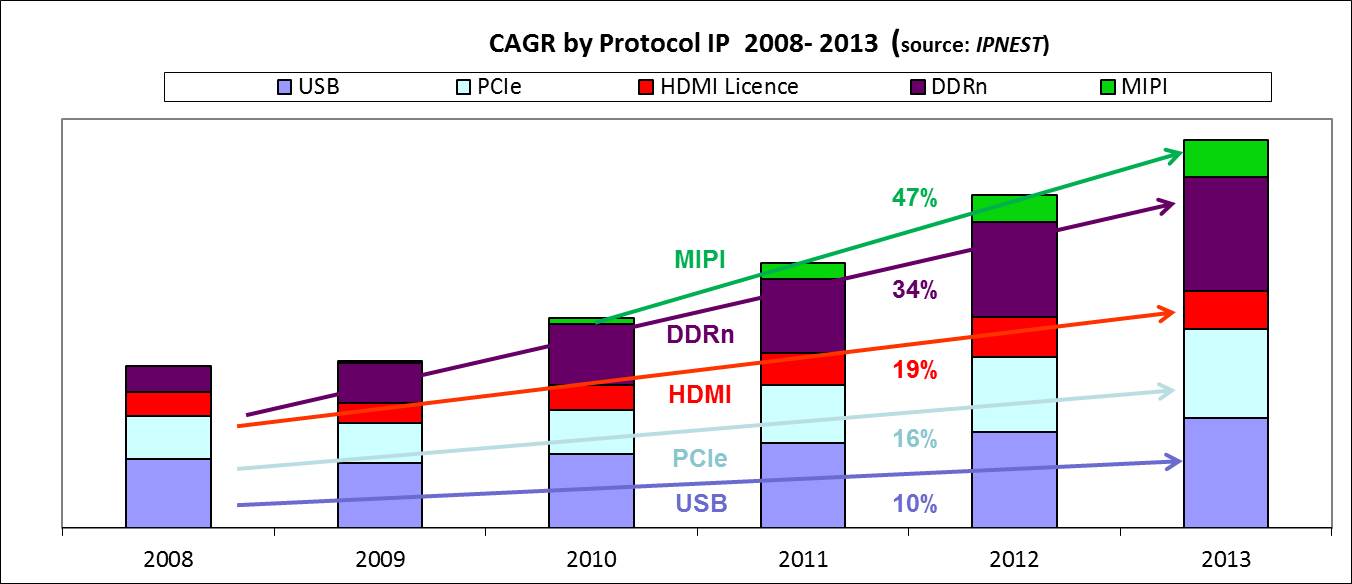

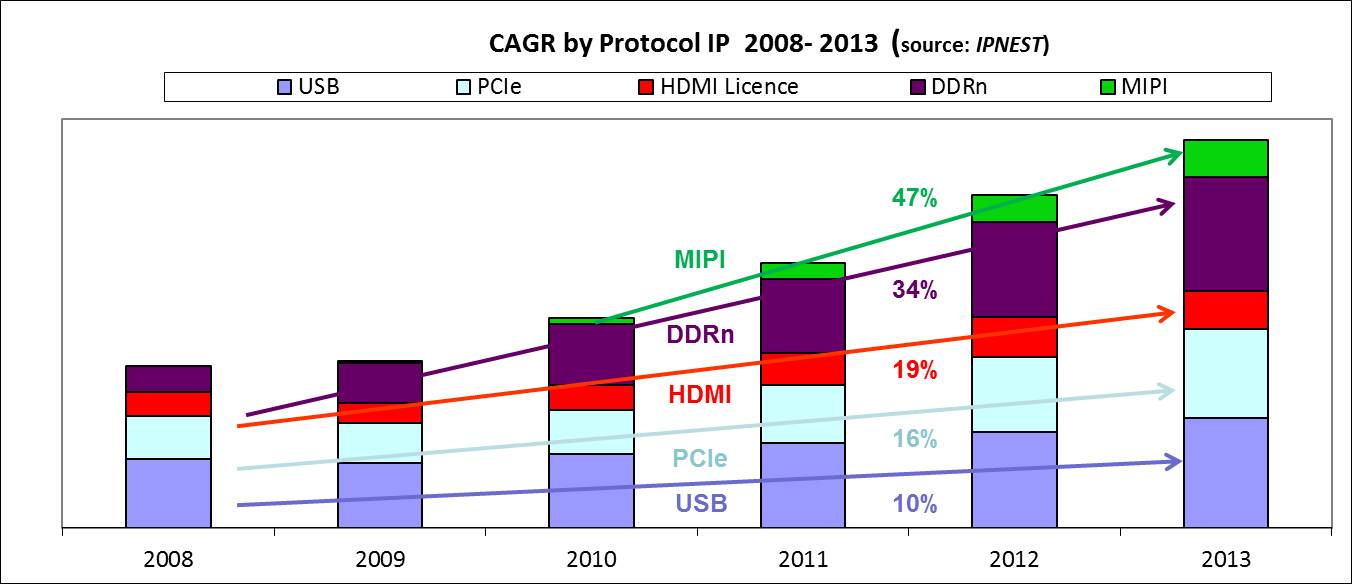

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying some interesting questions about MIPI or UFS. This graphic was presented, showing the strong MIPI IP business 47% CAGR (but MIPI IP is an emerging segment) and also the sustained growth of DDRn IP (DDRn IP market weighting almost $100 million, is already mature) with a 34% CAGR:

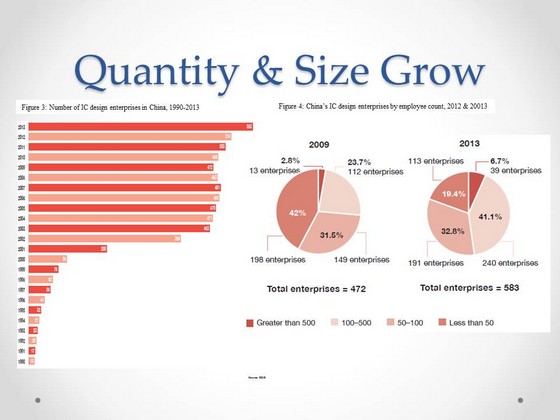

Let’s come back to the morning keynotes, with a presentation from Mark Ma, from Jiatao, a Shanghai based company representing various (western) IP vendors in China. Most of the slides are coming from a survey dedicated to the Semiconductor market in China, and these slides are worth to be carefully watched, you can go to D&R website for the complete slideshow “The Fortune behind Great Wall”. Just take a look at this one:

Between 2009 and 2013 the total number of China’s IC design enterprises has grown from 472 to 583. If in 2009, 42% had an employee count below 50 and 55% between 50 and 500, this last number has grown to 74% in 2013. The start-up share is decreasing, and this means that China’s IC design enterprises are successful, as they can grow in term of employee count. By the way, more than 540 mid-size IC design enterprise, most probably fabless is simply huge! How many of these can we count in the rest of the world?

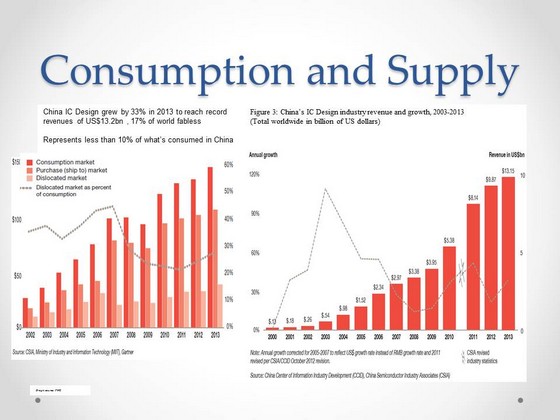

What does such number means for the IP business? Just that if an IP vendor doesn’t target China yet, he should do it as soon as possible! There should be many opportunities, as China’s IC design enterprises are only supplying in 2013 less than 10% of what’s consumed in China (this slide).

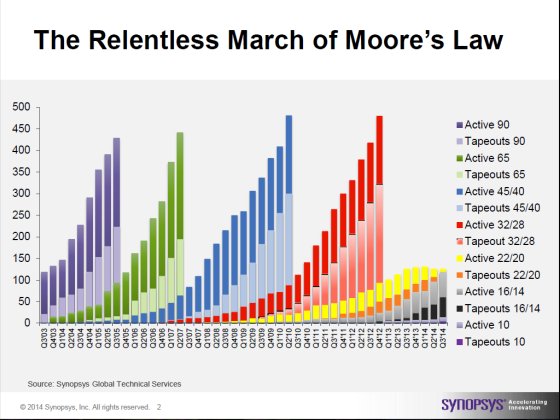

Synopsys and Cadence’s presentation are always very interesting. Both companies could decide to present their IP port-folio (that you can see on their web site), but Cadence and Synopsys have been creative and have presented attractive presentation. Let’s start with Synopsys and john Koeter sharing the active design and tape out count by technology node, for every quarter during the last ten years:

If anybody still has a doubt about Moore’s law landing around 20nm node, just take a deep look at this slide. You will see that the active design count has been in the 150-200 range per quarter for each node from 90nm to 28nm and that the cumulated active is higher for 40/45nm than 65nm. In fact, it took probably longer to design at 40/45nm than at 65nm, which stayed two years less on the curve than 40/45nm. Also very interesting is the number of Tapeouts for 16/14nm (in the 40 range) in Q3 2014, much higher than the Tapeouts count for 20/22nm in Q1 2013, at the highest level with 15 to 20. Clearly, the 20/22nm node will be skipped as the Tapeouts count in Q3 2014 is… zero!

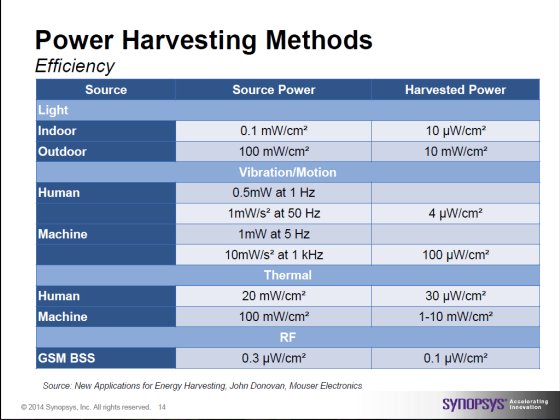

The above slide from Synopsys about Power Harvesting Method is an illustration of the creativity that I have above mentioned. I let you dig into the slide…

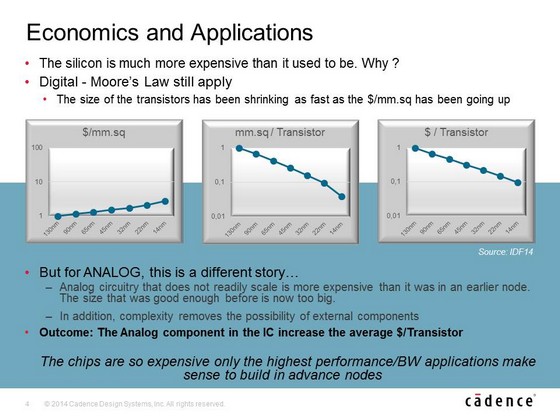

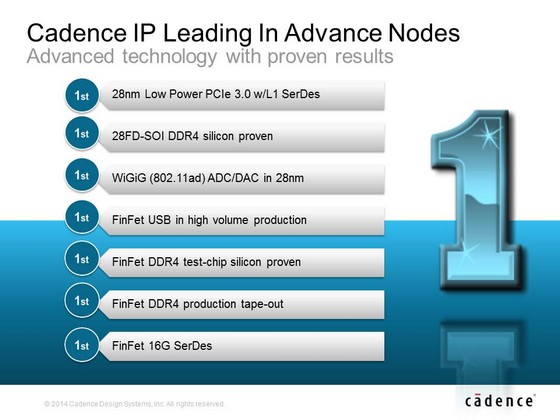

Amir Bar-Niv from Cadence has spent some time to explain the specificities of Analog, starting from the high level economics (above) to go down to analog design challenges in FinFet. The next slide is also interesting as it shows that Cadence is really committed to the IP business: this list of “1[SUP]st[/SUP]” includes from 28nm Low Power PCIe 3.0 SerDes to FinFet 16G SerDes… passing by Silicon proven DDR4 in 28nm FD-SOI. A clear illustration of what will be needed to build an IP ecosystem to support 28nm and 14nm FD-SOI technologies, but DDR4 is just a starting point…

From Eric Esteve from IPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.