Usually, we get the incremental story in news: this new release is x percent better at this or that than the previous release, and so on. Often missing is the big picture, telling how the pieces all tie together. Synopsys took on that challenge in their latest FPGA-based prototyping webinar.

We’ve been following this arc for a while, from beginnings in hardware to the latest software. Over the last year or so, Synopsys has talked at length about how their HAPS-70 system was created for big designs, and how the HAPS DX line could help with IP block verification and bringing reusable elements of prototyping forward. A few months ago, we looked at the debut of ProtoCompiler, a prototyping-aware FPGA synthesis tool with in-depth knowledge of optimization for the underlying platforms.

As Troy Scott opened his presentation with, this is a photo from a lab of a happy Synopsys customer – in the background are six HAPS platforms stacked together, giving roughly 300M gates of ASIC capacity. This isn’t just some theoretical concept; FPGA-based prototyping is delivering real-world results on a scale not possible just a couple years ago.

Scott walks through the four areas of prototype automation:

Scott walks through the four areas of prototype automation:

- FPGA logic synthesis for HAPS – the fundamentals of ASIC-to-FPGA migration;

- System planning – partitioning, high-speed pin multiplexing, system-level timing analysis;

- Debug and bring up – instrumentation, fault analysis, visibility;

- Transactor-based validation – APIs connected to host workstation and other tools.

One of the synthesis examples cited is the task of converting potentially hundreds of clock domains – not an unusual scenario when many IP blocks come from different sources – and gated clocks into a simpler clock enable scheme and dedicated spines typical of FPGAs. ProtoCompiler makes that a virtually automatic process, with reporting so designers can see what happened.

Another aspect of synthesis is language compliance and flexibility, with the implication that minimal changes are needed to use ProtoCompiler. Whether the design is in raw RTL, SystemVerilog, Verilog, or VHDL, it can be synthesized, complete with constraints and power management inferred from UPF. Using scripting, ProtoCompiler can also strip away circuits not needed for prototyping, or add debug probe points as desired.

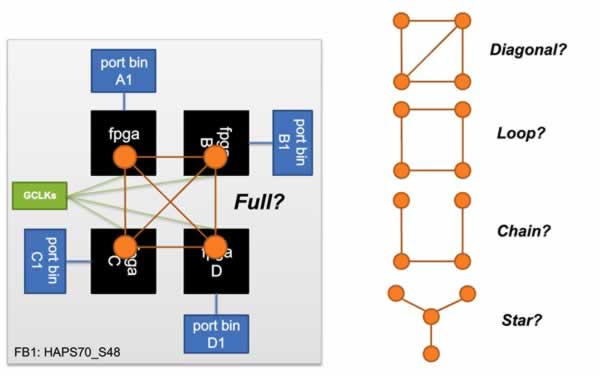

In planning, one of the tasks involves not only partitioning logic between multiple FPGAs, but choosing an optimal routing scheme between them. Scott uses a simple example of “port bins” to help define I/O, then asks the question of how interconnect topology should look. Defined in an abstract way, knowing roughly how many signals are involved, the partitioning engine can start a best fit.

Scott also shows how ProtoCompiler integrates with a Synopsys Verdi/Siloti design flow. Instrumentation can be inherited into the prototype flow using native file formats, or visibility can be increased around essential signals. Activity can then be correlated back into visualization and root cause analysis, and data can be expanded using a static solver to infer data not directly measured.

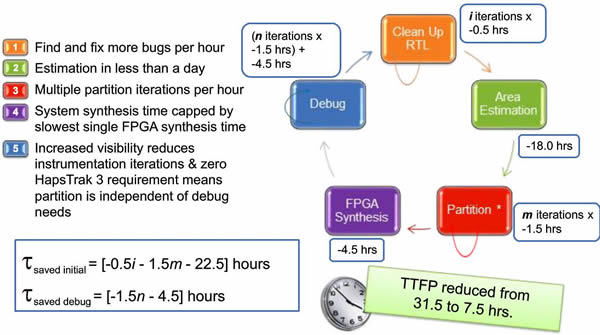

The result that Scott builds up to in his presentation is how everything works together to bring a prototype on line much faster. He walks through an example of savings, based on a large design experience, showing how significant results can be and the impact of reducing debug iterations.

These are just some highlights – the complete webinar is currently archived for viewing:

Synopsys ProtoCompiler Accelerates the Availability of the HAPS FPGA-Based Prototyping System

To me, this illustrates what was supposed to be the idea for EDA in the first place – cohesive flows that take advantage of knowledge from multiple phases of effort to produce results faster. Synopsys has been hard at work to bring FPGA-based prototyping into the mix not as just a physical realization tool, but as an integrated part of the synthesis-debug-verification flow.

Comments

There are no comments yet.

You must register or log in to view/post comments.