Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused by bad RAM chips after only 2 years of use, and my iPad 3 started rebooting multiple times per day with panics after 2 years of use. Ideally, you want to know during the design process that all sources of IC reliability are addressed, simulated and verified.

I had the chance last week to speak with Aveek Sarkar from ANSYS by phone about the topic of IC power noise reliability for FinFET designs. Aveek joined Apache back in 2003 which was then bought by ANSYS in 2011, and he is a VP of product applications. We had previously talked about how Apache used Distributed Multi Processing (DMP) to speed up full chip IR drop analysis in July 2013.

The RedHawk product has been used for at least a decade now to perform power, noise and reliability analysis of SoCs. What’s new is that the use of FinFET technology and higher capacity chips has created challenges that required updates to RedHaw. The big three drivers for such analysis tools has always been: Speed, Capacity and Accuracy.

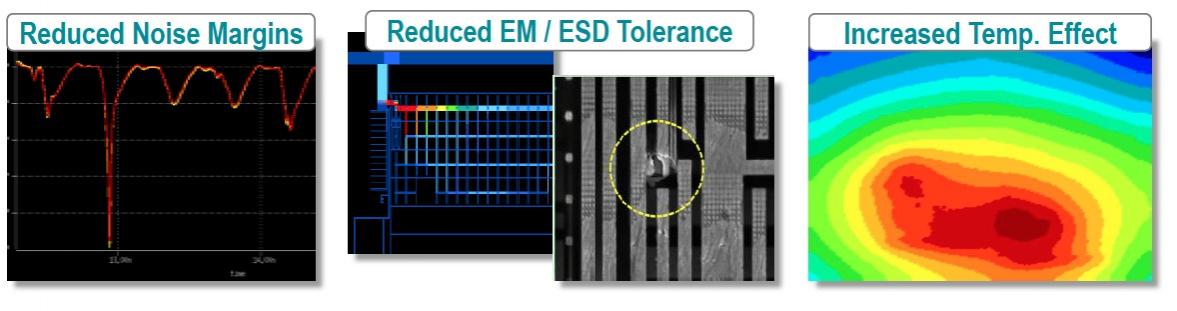

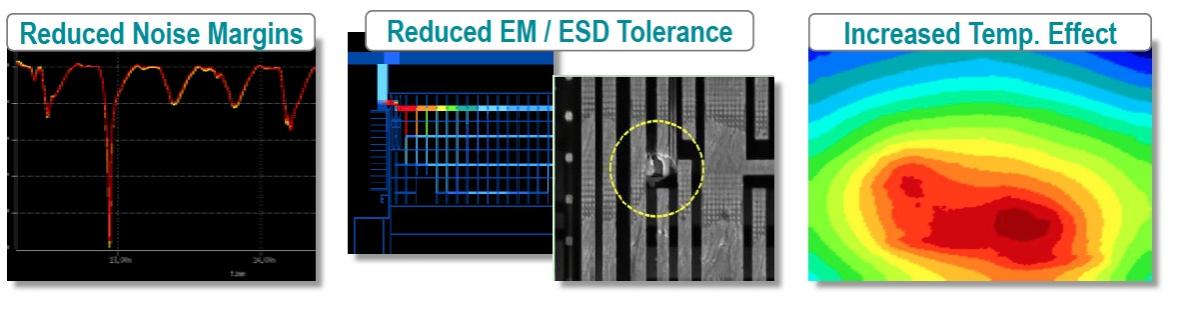

FinFET transistors have attracted much attention because they have improved performance, reduced power and higher device densities. Even the FinFET circuit delays have lower variations to VDD changes than bulk CMOS transistors do. On the other hand, FinFET devices also have reduced noise margins, EM and ESD failures are more likely plus higher temperatures impact reliability.

With FinFET transistors the power noise is increasing, so it’s even more critical that you perform accurate analysis during the design phase. Idsat values are higher, and reducing Vdd to 700mv reduces the noise margin even smaller, so in general FinFET devices tend to be noisier. The two design methods to deal with this are: Reduce noise levels or add more decoupling capacitors. A power noise analysis tool must be run on the entire chip+package+board to get accurate answers, instead of using a simplified approach that decouples these three design levels and may leave you with wrong answers.

The latest release of the RedHawk tool was just announced and it’s called RedHawk 2014, and here’s what to expect:

- About a 3X speed-up improvement using the DMP approach

- 2.5X reduction in peak RAM usage

- Capacity to handle multi-billion transistor designs

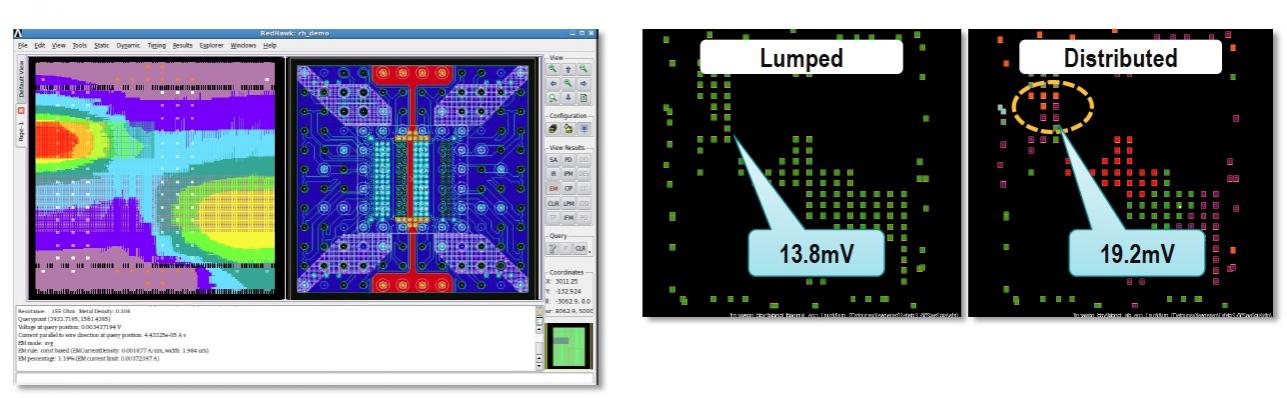

It’s recommended to run the package and chip-level voltage drop analysis and optimization concurrently, and the new tool option that enables this is called RedHawk-CPA. If you run voltage drop analysis at the chip level and assume that the package model can be simplified as a few lumped elements, then the analysis numbers returned are going to be overly-optimistic which will create a false sense of security when in fact you may have failures.

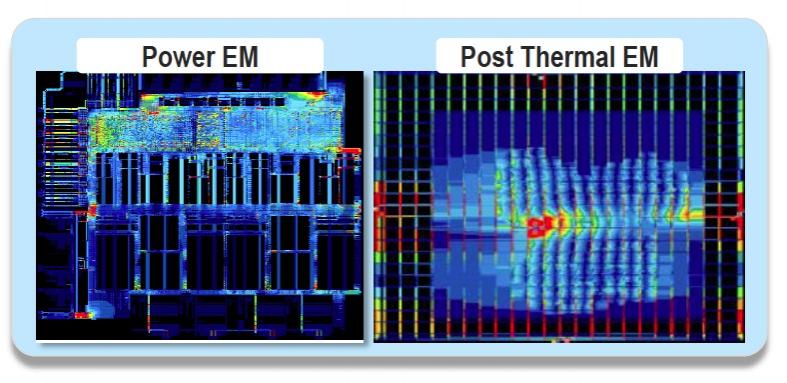

Electromigration (EM) is another reliability concern for ICs at 20nm and lower nodes, and EM rules effect the size of wire routing, via sizes and even the layer choices. I saw my first EM failures at Intel while designing DRAMS in 5um NMOS technology, so EM concerns have been around for decades. RedHawk provides EM analysis and helps to pinpoint EM violations by showing you a colorized layout view where Red areas are failing, requiring the IC designer to start taking corrective action, then re-run the EM analysis tool until compliance is reached.

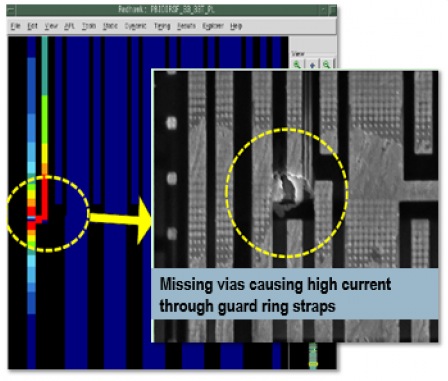

Finally, Electro-Static Discharge (ESD) is another reliability issue that all ICs must be designed for protection. A designer would add diodes to prevent ESD damage. The PathFindertools helps you to find ESD violations, then it’s up to you to apply a fix and re-simulate. Here’s an actual photo of an ESD failure provided by Samsung at the 2013 International ESD Workshop, and next to it on the left shows how the PathFinder tool identified this exact area in the layout as being most susceptible to ESD failure.

TSMC has already certified the RedHawk 2014 tool for their FinFET process called 16N v1.0: extraction, rule handling, IR drop, EM analysis.

Summary

ANSYS has a lot of credibility and momentum in this area of IC power, noise and reliability analysis, now supporting FinFET technology. Existing RedHawk users receive the RedHawk 2014 release as part of the maintenance, while the RedHawk-CPA tool is a new, optional add-on. I plan on visiting ANSYS at DAC to learn a bit more, so expect a blog from my San Francisco trip next month.

lang: en_US

Share this post via:

Comments

0 Replies to “IC Power Noise Reliability for FinFET Designs”

You must register or log in to view/post comments.