It feels to be at the top of semiconductor technology by having dies with high density of semiconductor design at sub-20nm technology node stacked together into a 3D-IC to form a complete SoC which can accommodate billions of gates. However there are multiple factors to be looked at in order to make that successful amid often conflicting goals of power, performance and price. 3D-IC architecture provides large integration possibilities that can help meeting power and performance goals; however DvD (Dynamic Voltage Drop) hotspots need to be managed well along with full chip-package level analysis. Again emerging technologies such as reduced supply voltage (sub-1V), DVFS (Dynamic Voltage and Frequency Scaling), MTCMOS (Multi-Threshold CMOS) and LDO (Low-dropout voltage regulator) are being used to meet stringent low power demand while trying to meet performance and reliability goals. Reduced supply voltage (that reduces noise margin) along with high density of functionality and high operating speed induces significant noise into the system and that initiates the need to accurately model power/ground noise in the system to determine right levels of operating speed and voltage.

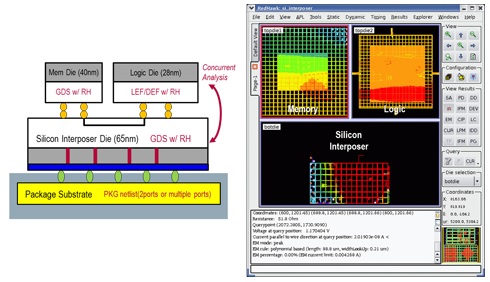

I was impressed with Apache’sRedHawk-3DX solution which is apt at handling these issues at sub-20nm and provides a right platform for power integrity analysis and sign-off for 3D-ICs that may accommodate billions of gates and operate at clock speed beyond 3 GHz. In order to accurately model and simulate power/ground noise, complete extraction of on-chip as well as package and PCB parasitics is done with due consideration to TSVs (Through Silicon Vias), interposer and micro-bumps. APL (Apache Power Library), on-chip inductance modeling, support for multi-port broadband S-parameter package/PCB netlists and EM modeling in RedHawk-3DX advances the accuracy levels at sub-20nm nodes.

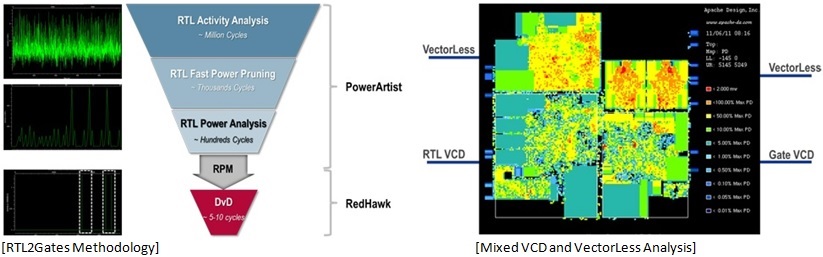

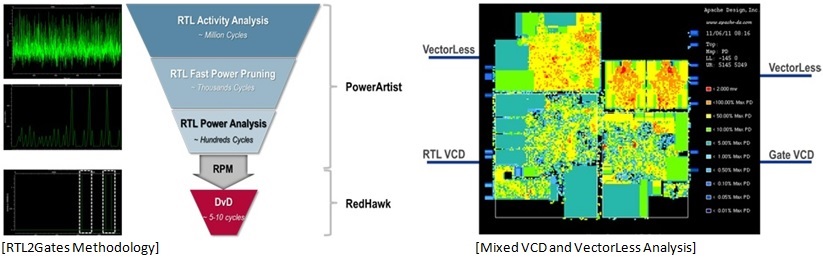

Accuracy and coverage of dynamic power analysis has been enhanced by the novel idea of ‘event’ and ‘state’ propagation techniques which utilize both, functional stimulus and statistical probabilities to determine the switching scenario in the design. RTL2Gates methodology is realized by utilizing a fast event propagation engine and RTL VCD at RTL level without requiring gate level vectors. Critical cycles with peak power are identified by using RPM (RTL Power Model) which equip the logic engine to determine the switching state of the complete design for cycle accurate DvD analysis. A state propagation engine uses toggle activity (at primary IOs, register outputs etc.) as input and a smart ‘detection and pruning’ technique to eliminate the traditional problem of underestimating toggle rates in the logic cone. The predicted toggle rates are used by RedHawk-3DX to perform time-domain VectorLess analysis. RedHawk-3DX also supports a mixed-mode, where part of the blocks use RTL or gate level VCD as available and rest of the blocks remain VectorLess to derive switching activity, thus enabling designers to perform accurate full-chip dynamic power noise simulation.

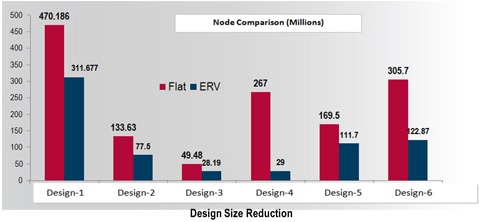

Since the PDN (Power Distribution Network) is shared across the chip or complete package, full-chip capacity along with package/PCB model inclusion is a must for accuracy of simulation results. RedHawk-3DX has ERV (Extraction Reuse View), a unique hierarchical extraction and modeling technology that delivers full-chip capacity and performance without sacrificing the sign-off accuracy. Additionally, techniques such as MPR (Mesh Pattern Recognition) and multi-threading are used to reduce physical memory and run-time.

LDOs can be seen in most SoCs as they provide more robust power supply to noise-sensitive parts of the design. However, model of a chip with LDO must capture all key operating behaviors of the LDO, including the change in its output supply voltage for different load current scenarios. The expanded low-power simulation capabilities of RedHawk-3DX enable creation and use of such models in full-chip power noise analysis.

[3D-IC Voltage Drop using Multi-Pane GUI]

Designers can analyze 3D/2.5D designs either in concurrent mode which simulates full layout details for all dies including interposer, or in model-based mode which uses CPM (Chip Power Model) to capture the electrical signature (current and parasitics) for some chips whose layout may not be available. Design architects can explore various design configurations for early prototyping of such complex structures. The multi-tab, multi-pane GUI provides great flexibility in analyzing multi-die designs by simultaneously projecting DvD hotspots and other results of multiple dies in various combinations.

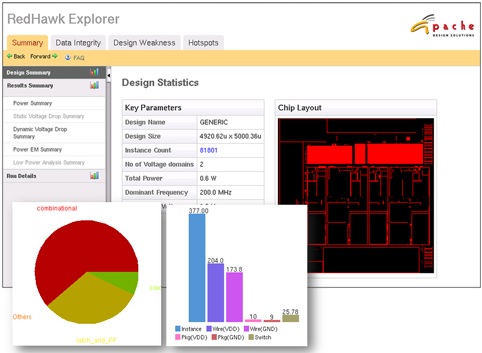

RedHawk Explorer helps designers to qualify the input data, review design weaknesses, debug specific hotspots and provide feedback for design improvements. It provides concise summary of various analysis results. With its powerful cross-probing capabilities designers can easily locate, isolate, understand and resolve various power integrity issues.

It’s interesting to see RedHawk’s comprehensive chip-package-system level analysis environment which can enable designers to do package-aware IC simulation as well as chip-aware package/PCB simulation. A detailed technical paper is available at Apache’s website here.

More Articles by Pawan Fangaria…..

lang: en_US

Share this post via:

Comments

0 Replies to “How to meet 3Ps in 3D-ICs with sub-20nm Dies?”

You must register or log in to view/post comments.