Since Synopsys acquired Eve over a year ago, they haven’t announced anything new in the ZeBu product line. Emulators are not like software where you expect incremental releases a couple of times per year, each new “release” is a complete re-design using new hardware fabric in a new process technology. Earlier this week Synopsys announced Zebu Server-3, currently the industry’s fastest emulation system (to be fair, whenever a new emulation product is announced it tends to be the fastest for a time…). They also announced a collaboration with Imagination Technologies to enable faster emulation, currently for Imagination’s PowerVR GPUs and in the future for the MIPS processor line too. Imagination are achieving clock speeds of 3.5MHz emulating their GPUs, compared to historic speeds closer to 1MHz with earlier generations of emulators.

Since Synopsys acquired Eve over a year ago, they haven’t announced anything new in the ZeBu product line. Emulators are not like software where you expect incremental releases a couple of times per year, each new “release” is a complete re-design using new hardware fabric in a new process technology. Earlier this week Synopsys announced Zebu Server-3, currently the industry’s fastest emulation system (to be fair, whenever a new emulation product is announced it tends to be the fastest for a time…). They also announced a collaboration with Imagination Technologies to enable faster emulation, currently for Imagination’s PowerVR GPUs and in the future for the MIPS processor line too. Imagination are achieving clock speeds of 3.5MHz emulating their GPUs, compared to historic speeds closer to 1MHz with earlier generations of emulators.

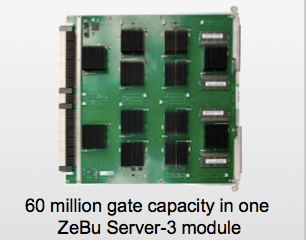

ZeBu servers come in a 20″ cube weighing 155lbs and consuming less than 2.5KW. Inside there are Zebu modules (boards) that each handle 60 million gates. A cube can hold 5 of them and so each one can handle 300M gates. Ten of the cubes can be chained together to give a total maximum capacity of 3B gates. The underlying fabric is Xilinx Virtex-7 arrays, the ones that you have probably heard a lot about if only because they are 2.5D interposer-based designs using through silicon vias (TSVs). They are built in TSMC’s 28nm process.

ZeBu servers come in a 20″ cube weighing 155lbs and consuming less than 2.5KW. Inside there are Zebu modules (boards) that each handle 60 million gates. A cube can hold 5 of them and so each one can handle 300M gates. Ten of the cubes can be chained together to give a total maximum capacity of 3B gates. The underlying fabric is Xilinx Virtex-7 arrays, the ones that you have probably heard a lot about if only because they are 2.5D interposer-based designs using through silicon vias (TSVs). They are built in TSMC’s 28nm process.

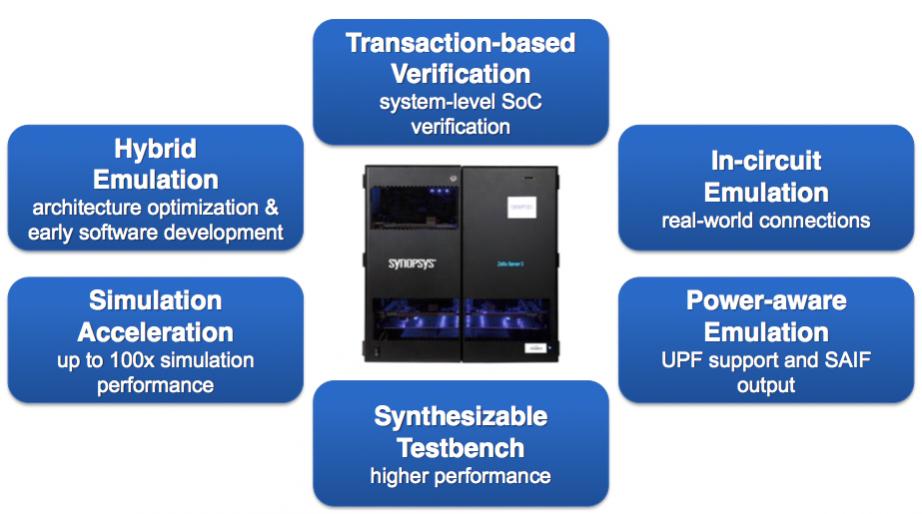

Every emulation announcement rides on Moore’s law and is faster and with higher capacity than the previous generation. Perhaps more interestingly is the verification technology that Synopsys has intetgrated in with the Eve emulation technology they acquired. Here are some of the technologies that surround Zebu Server-3:

- transactor libraries

- memory models

- DesignWare

- Simulator-like debug with Verdi[SUP]3[/SUP]

- Waveform viewing

- Autotrace to disk

- Coverage measurement

- In-circuit I/O

- Virtual adaptors

- Automated software flow: partition, P&R, synthesis, memory compilers

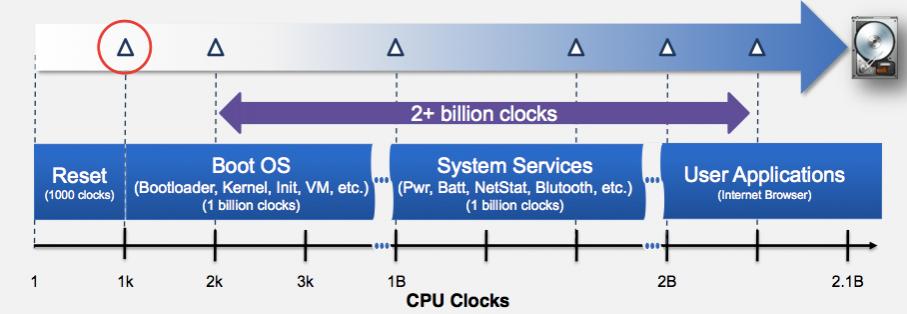

One major challenge they have addressed is hardware/software co-verification. One problem in this environment is that the time between a bug in software and something detecting it might be a couple of billion clock cycles. A problem during a Linux boot might not show up until an attempt is made to access a video encoder, for example. Traditionally, emulators would capture a moving window of a couple of million vectors but that is not enough. Instead, ZeBu captures the state periodically and captures all inputs. To go to any clock cycle requires reloading that state and rerunning the inputs to get to the clock cycle of interest. This way billions of cycles can be stored very efficiently (interestingly, this is almost the same approach as we implemented at Virtutech to enable us to run code backwards. A reverse single-step meant reloading state and running all instructions except one).

They can also do hybrid emulation, with part of the design running on a virtual platform and part in the emulator. Where models exist (especially CPU models) they will typically run faster on the platform. A CPU “model” is a bit of a misnomer, since it is really a JIT compiler that can run the emulated code at close to (sometimes above) the actual performance of the target microprocessor. But emulation seems to be the killer-app for virtual platforms, avoiding the problem of needing to create a lot of models and keep them accurate as the RTL is developed. Just run the actual RTL on the emulator.

I assume you will be able to see a ZeBu Server-3 on the Synopsys booth at DVCon next week. They are at booth 201.

The Zebu press release is here.

More articles by Paul McLellan…

Comments

There are no comments yet.

You must register or log in to view/post comments.