The Seattle Seahawks had an awesome victory in the SuperBowl against the Denver Broncos, so folks living here in the Pacific Northwest are feeling proud and optimistic. The recent DesignConconference and exhibit ended 10 days ago and there were also victors announced in terms of the annual DesignVision awards that have three criteria:

[LIST=1]

Since DesignCon is a diverse event there are actually multiple categories to enter for the DesignVision award:

- Design Verification Tools

- IC Design Tools

- Interconnect Technologies & Components

- PCB Design Tools

- Semiconductor & IP

- Semiconductor Components and ICs

- Test & Measurement Equipment

Four of the companies that won an award I had heard about before: ANSYS Inc, Altera, Microsemi and Altium.

[TABLE] style=”width: 500px”

|-

| Category

| Company

| Product

|-

| Design Verification Tools

| Altera

| ARM DS-5 Altera Edition Toolkit

|-

| IC Design Tools

| ANSYS

| Pathfinder Dynamic

|-

| Interconnect Technologies & Components

| FCI

| ExaMAX Direct-Mate Orthogonal Connector

|-

| PCB Design Tools

| Altium

| Altium Designer 14

|-

| Semiconductor Components

| Microsemi

| IGLOO2 FPGA

|-

| Semiconductor and IP

| Altera

| Stratix 10 FPGAs and SoCs

|-

| Test & Measurement Equipment

| PicoTechnology

| PicoScope

|-

Today I spoke with Norman Chang of ANSYS to better understand why Pathfinder Dynamic won a DesignVision award this year.

Q: What does the PathFinder Dynamic tool do, and who uses it?

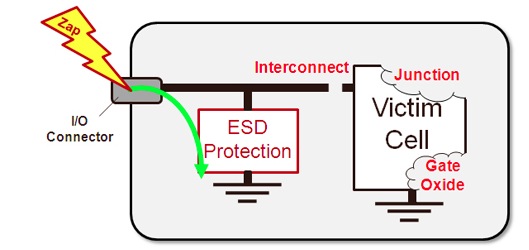

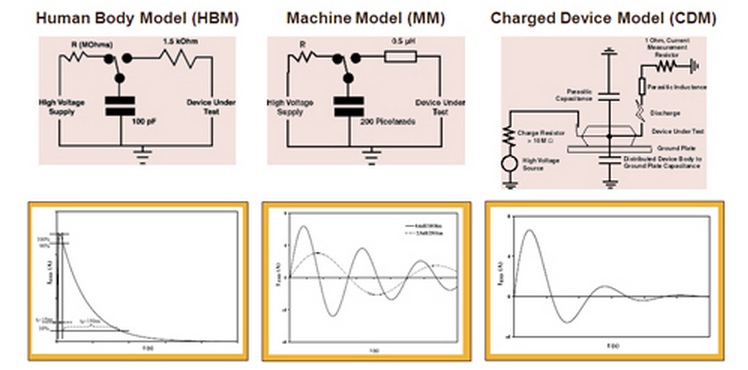

PathFinder Dynamic address on-chip ESD through checks of HBM (Human body model), Charged Device Model (CDM) and Machine Model (MM). The approach is a transient simulation, where a netlist of your chip is extracted with the metal grid of power, ground, and well diodes between P-well and N-well (parasitic diodes).

Q: When do you run this extraction and simulation?

You must wait until the end of IC implementation. This tool reads in your GDS II layout, then a netlist is extracted.

Q: Why is dynamic ESD simulation required?

Because secondary discharge paths are caused by parasitics of well diodes, reverse junctions are unintended discharge paths. We can now detect the stress on every junction and currents through all diodes, as a function of time. Both the amplitude and duration of the waveforms are analyzed.

Q: Does the design supply any input stimulus?

No, the designer doesn’t supply any input stimulus, the tool understands how to stress for ESD checks. The foundry supplies some substrate information used for ESD simulation, resistances and capacitances used to created a 3D mesh of the substrate.

Q: When was this tool announced?

We reached production ready just recently, however it’s been in beta testing for awhile. Nvidia did a joint paper in Sep 2012 at the ESD Symposium for HBM and CDM.

Q: What kind of damage does ESD do to my SoC?

Gate oxide ruptures can be caused by multiple ESD mechanisms which in turn changes the MOS device characteristics. We’ve run our dynamic tool and actually correlated it with Silicon failures.

Q: Who would use PathFinder Dynamic?

Foundries will use this tool when creating IO cells. Customers will run it on their own SoC designs.

Q: Is this tool in the TSMC reference flow yet?

Not quite, we’re working to get Dynamic in the TSMC Reference Flow, stay tuned for news.

Q: What other tool does ANSYS offer for ESD checking?

We also have the Pathfinder static tool, where the checks are for static Resistance and Current density values. These are called intentional discharge paths, and they are validated by checking forward-biased diodes.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.