I will share with you the most interesting I have heard during IP-SoC 2010, last December in Grenoble. Today, let’s summarize what I heard about the future of the IP business. The presentation was done by Gartner, in the “Auditorium” (largest room). It first started with the results for 2010, and I took some notes, as you can see the business figures are very informative:

Overall IP business growth (2010/2009) was +24.8%, for a total of $1677M

- IP licensing (50% of total) grew by 20%, royalties (42%) grew by +31% and maintenance/services (8%) by 25%.

This “forecast” is useful, as well as some trends proposed by Gartner about the IP market:

- Innovation is moving from chip level to system level was the clear message. Or, if you prefer, be prepared to provide not only a piece of H/W to be used within a chip, but a more complete solution integrating several pieces of H/W, the drivers for these, and the S/W at system level. (We will come back to this in a next post).

- In Automotive and Industrial, the IP usage will be growing from being 5 to 10% of a chip to 30 to 40% within 3-5 years.

- In Wireless, IP usage will double and pass from 20% today to 40% in 2013/14.

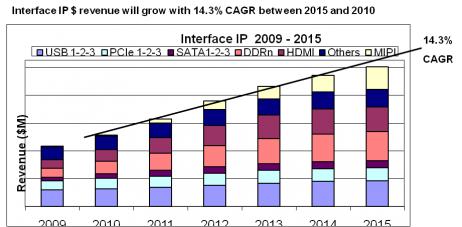

Good to hear, this means that the IP market, as a business, should be growing in value per license (moving from chip to system level) and in license number, as the IP usage is strongly growing in at least two segments. Then came the growth forecast for 2011 to 2014. Don’t worry, I will share it with you:+6% in 2011, then +2.3% in 2012, followed by +6.7% in 2013 and 6.9% in 2014.Here I disagree! How cans a certain market strongly grow in unit value and in unit count, and posts a mere 5.8 CAGR ? I know the number of ASIC/ASSP design starts is expected to go down, but only by 2 or 3% per year. And the FPGA design starts also generate license sales (another post will come, as I have attended to the FPGA panel, see: http://www.design-reuse.com/ipsoc2010/program/panel_fpga.htmlSo I decided to dig into these figures, here is that I found.Using the forecast for 2010-2015 I have built for the Interface IP market(see: http://www.ip-nest.com/index.php?page=wired)analyzing precisely USB, PCIe, HDMI, DDRn, SATA, MIPI and a few others protocols, I have built this table. For 2010/2015, the CAGR is: 14.3%Using Gartner’s figures above listed, I have built a similar table, including all the IP segments. .

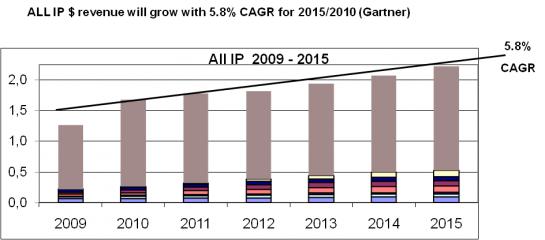

For 2010/2015, the CAGR is: 14.3%Using Gartner’s figures above listed, I have built a similar table, including all the IP segments. . For 2010/2015, the CAGR is 5.8%Now, extracting the expected market growth for all the IP businesses: Processor, Memories, Libraries, Mixed Signal, Digital… everything at the exception of the Interface IP, becomes pretty simple (no problem, I give you the formula: when a = b + c, then b = a – c; rocket science!). So the new table:

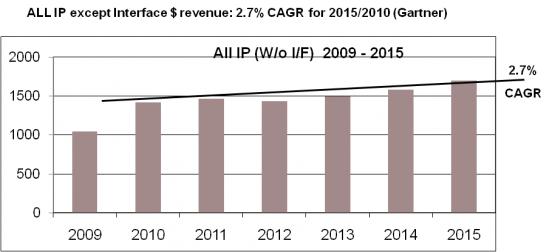

For 2010/2015, the CAGR is 5.8%Now, extracting the expected market growth for all the IP businesses: Processor, Memories, Libraries, Mixed Signal, Digital… everything at the exception of the Interface IP, becomes pretty simple (no problem, I give you the formula: when a = b + c, then b = a – c; rocket science!). So the new table: the CAGR is now 2.7% !!What do you think? Is it realistic to expect a growth rate between 2 and 3% for a certain market, when everybody says the IP usage will grow (double?) because that is the only way to guarantee the TTM, for ASIC, ASSP and also FPGA?I really would appreciate your comments about this!

the CAGR is now 2.7% !!What do you think? Is it realistic to expect a growth rate between 2 and 3% for a certain market, when everybody says the IP usage will grow (double?) because that is the only way to guarantee the TTM, for ASIC, ASSP and also FPGA?I really would appreciate your comments about this!

The Data Crisis is Unfolding – Are We Ready?