It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending the short webinar of about 30-40 minutes, presented by Anne Merlande of ST in a very simplistic way. One of the attractions of the webinar is an exciting video which speaks about the advantages of FDSOI technology over bulk architecture along with some simple experiments; FDSOI is simpler and provides significantly improved device performance, power efficiency and lower temperature, ideal for smart phones that have longer battery life and cooler to handle.

Now let’s see ST’s experience with Apache’sPowerArtist and ARMCores. I am just outlining some of these; details can be looked at in the webinar. I don’t have to mention much about ST’s long relationship (of about 17 years) with ARM and ST being lead partner with ARM on A15 and A57. Recent focus has been on low power and high performance.

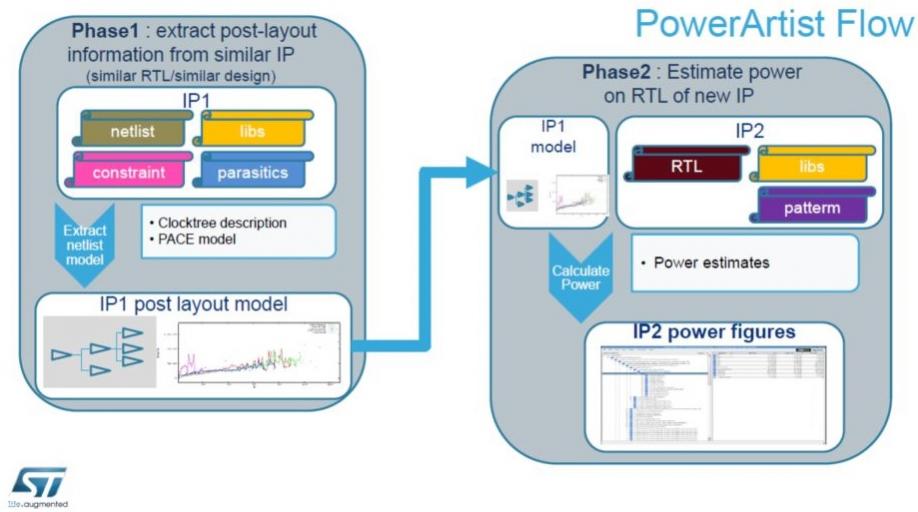

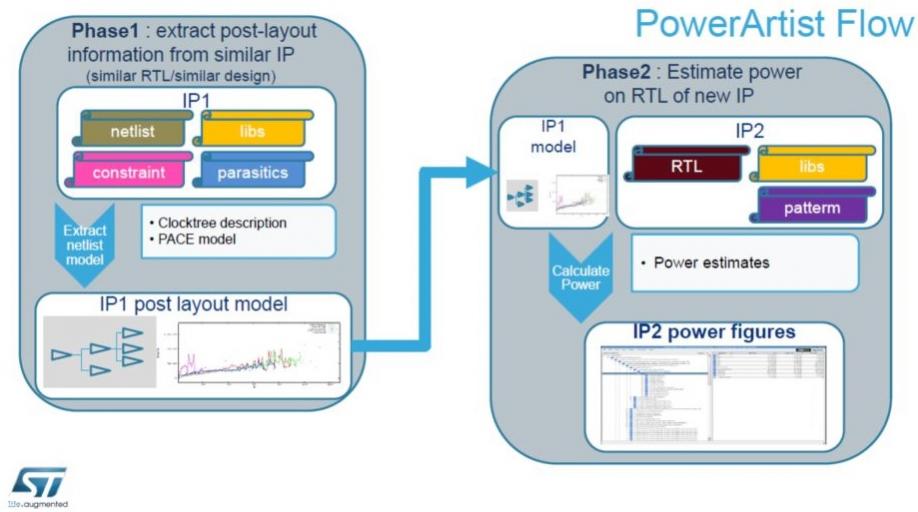

ST uses PowerArtist at RTL level to determine the best architecture and implementation strategy to gain in dynamic power saving, thermal and power integrity analysis, SMPS sizing and power optimization of ST IPs embedded into ST ARM sub-systems. By doing this, they are able to significantly save time in attaining power sign-off stage. How about accuracy? Let’s see.

[The flow used at ST for PowerArtist calibration]

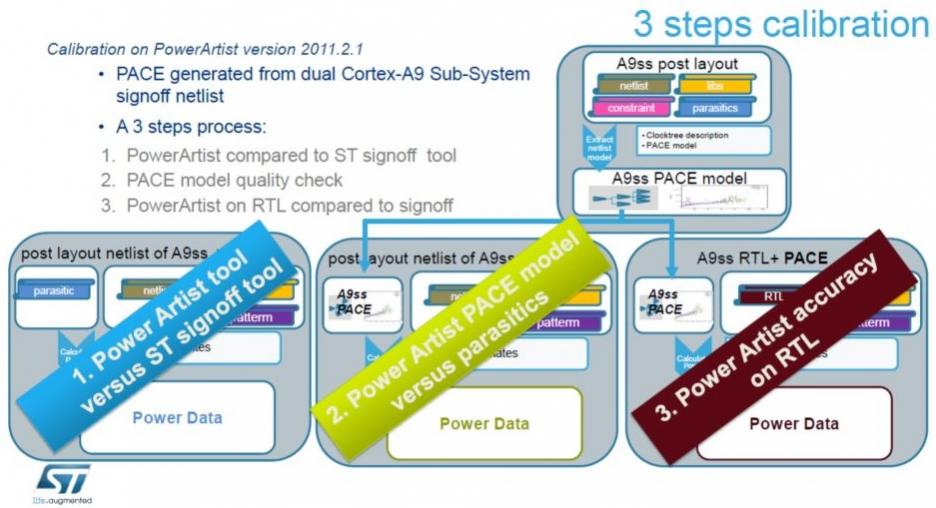

[PowerArtist calibration on Dual Cortex-A9 sub-system (A9ss)]

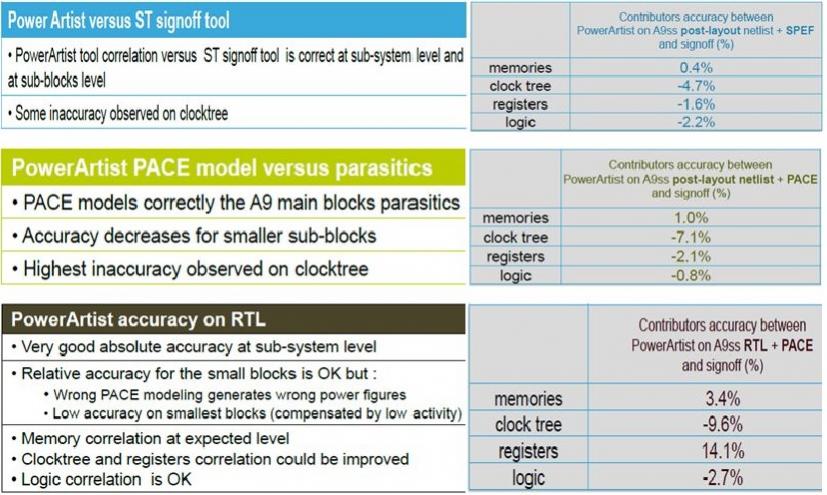

Block level accuracy between PowerArtist on A9ss and ST sign-off was compared at all 3 stages – i) post-layout netlist using SPEF, ii) post-layout netlist using PACE and iii) RTL using PACE.

[Correlation data at post-layout netlist+SPEF, post-layout netlist+PACE and RTL+PACE stages]

Similarly, ST verified block level accuracy between PowerArtist on Dual Cortex-A15 sub-system at RTL using A9ss-PACE and post-placed netlist. It is observed that PowerArtist accuracy at RTL level is within acceptable limits. Clocktree inaccuracy is relatively higher as this is good for timing but bad for dynamic power. Correct PACE (Power Artist Calibrator and Estimator) models provide correct accuracy levels.

Power integrity patterns are developed by running simulation at RTL level and adjusting power window to identify the best window to get the maximum current slope. This eliminates the need of gate level simulation.

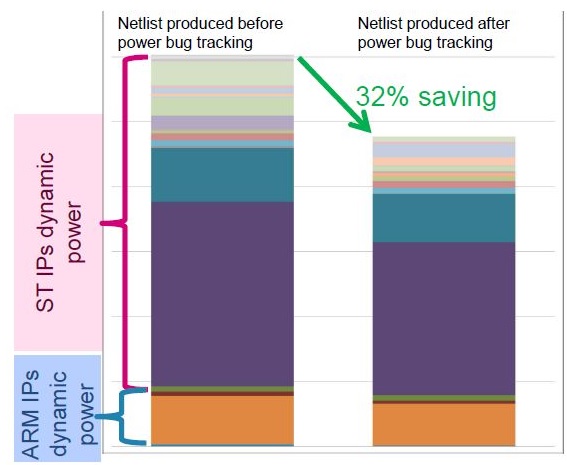

By using PowerArtist’s power exploration capabilities, ST is able to detect power bugs early in the cycle and save more than 30% power.

[A15ss low-power use case dynamic power]

PowerArtist enables power convergence and tracking of power along with RTL development.

Overall, PowerArtist has been seen to significantly shorten the design cycle with its power prediction and verification capabilities at RTL level, accurately and efficiently. Power bugs can be identified and corrected at RTL level, thus improving design (chip) reliability. It’s worth attending the webinar and knowing more.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.