Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one process generation to the next which means that transistors do not turn off completely. This is an especially serious problem with FPGAs since they have a huge number of transistors, many of which are not actually active in the design at all, just due to the nature of how an FPGA is programmed.

Power dissipation is related to thermal because heat dissipated rises with power. But temperature is related to reliability: every 10°C increase in temperature doubles the failure rate. There are all sorts of complex and costly static power management schemes but ideally the FPGA would simply have lower static power. TSMC, which manufactures Xilinx FPGAs, has two 28nm processes, 28HP and 28HPL. The 28HPL process has some big advantages over 28HP:

- wider range of operating voltages (not possible with 28HP)

- high-performance mode with 1V operation leading to 28HP-equivalent performance at lower static power

- low-power mode at 0.9V operation, with 65% lower static power than 28HP. Dynamic power reduced by 20%.

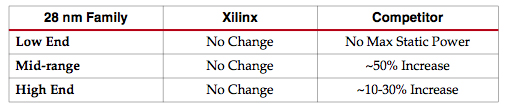

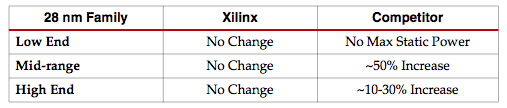

The 28HPL process is used to manufacture the Xilinx 7 series FPGAs. The net result is that competing FPGAs built in the 28HP process have no performance advantage of series 7 and some of the competing products come with a severe penalty of over twice the static power (along with the associated thermal and reliability issues). In fact Xilinx’s primary competitor (I think we all know who that is) has had to raise their core voltage specification resulting inn a 20% increase in static power and their power estimator has gradually crept the power up even more. Xilinx has invested resources so that the power specifications published when the product is first announced do not subsequently require being revised, meaning that end-users can plan their board design confident they do not need to worry about inaccurate power estimates.

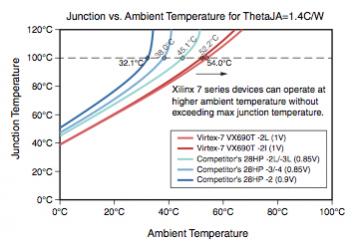

The low power and associated thermal benefits mean that Xilinx FPGAs can operate at higher ambient temperature without the FPGA itself getting too hot. The graph below shows junction temperature against ambient temperature for series 7 standard and low power devices compared to the competitor’s equivalent array. This is very important since the ability to operate at 50-60°C ambient temperature while keeping the junction temperature at or below 100°C is essential in many applications, such as wired communications designs in rack-style environments such as datacenters. It is no secret that routers and base-stations are one of the largest end-markets for FPGAs.

But wait, there’s more, as the old infomercials said.

Not specific to series 7, the Vivado Design Suite performs detailed power estimation at all stages of the design, and has an innovative power optimization engine that identifies excessively power hungry paths and reduces them.

Reducing dynamic power depends on reducing voltage (which the 28HPL allows), reducing frequency (usually not an option since that is set by the system performance required) or reducing capacitance. By optimizing the arrays for dense area, meaning shorter wires with lower capacitance, power is further reduced compared to Xilinx’s competitors.

And there is even more than that. But to find out you need to download the Xilinx white paper Leveraging Power Leadership at 28nm with Xilinx 7 Series FPGAs available here.

Share this post via: