At DAC you can measure buzz by how many people are crowded into your booth. I saw a crowd at the Oasys booth, so stopped to take in their 10 minute overview presentation. Here’s what I learned.

Implementation Issues Oasys resolves:

Generates an initial floorplan as guidance to P&R team

Elminates routing congestion

PPA improvment of your IP

Constraints debugging

Implement what if exploration

Fast path to implementation.

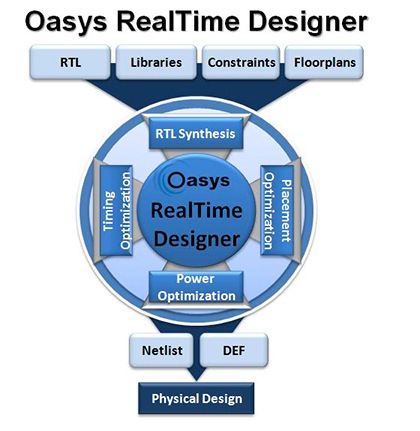

Overview: 2009 physical RTL synthesis, also used by Xilinix Vivado tool

Intel Capital & Xilinx investors

Oasys Synthesis: Unlike traditional RTL synthesis, gate-level optimization.

– RTL level optimization to give 10X TAT, capacity to synthesize top-levle of any dsing.

– Placement has biggest impact on timing. Place first methodology.

– RTL synthesized into a virtual partition, then placed gates.

– One db from RTL to placement, physical cross-probe between RTL/Gates/Placement

– Find timing violations and find the RTL source code and placement in floorplan, saves hours of time

– Initial flooplan? RealTime flooplan compiler. Not 6 weeks, but just hours.

– Place first methodology is unique, and in 1-2 days you have an optimal placement, hand off to P&R team

– Is my design ready for implementation?

– Creates floorplans, timing maps, dynamic & static power maps, routing congestion.

– Identify congestion, caused by a mux with 2,000 wires.

– Have I met my power budget?

– Dynamic and Static power estimates early in the design process. Other tools are approximate in power.

– How do you know this is the best implementatin option?

– Not enought time to explore synthesis options?

– With Oasys you can explore the design space, many options, not just a few. Did I meet my PPA requirements?

How do you implement your design?

RealTime Designer – Run on production chips, up to 10X faster TAT, 100M+ gate capacity, good starting point to P&R.

Equivalency Checker – RealTime Parallel EC. RTL to gates verification.

*lang: en_US

Share this post via:

The Data Crisis is Unfolding – Are We Ready?