If you design with ARMCores and need to estimate dynamic power early in the flow, then consider what STMicroelectronics has done with their high performance, power-efficient subsystems. Anne Merlande is a Processor Micro Architecture technical expert, and will be presenting in Booth #1346 at DACon June 4th, 2:00PM. Her topic is: STMicroelectronics: RTL Power Estimation on ARM Core Sub-systems. You have to register for this suite session.

Anne Merlande, STMicroelectronics

I contacted Anne by email this week to get some more insight into the design challenges and approaches that they are using.

Interview

Q: What kind of SoC designs does your group work on?

We are building High Performance Power efficient Subsystems based on ARM processors

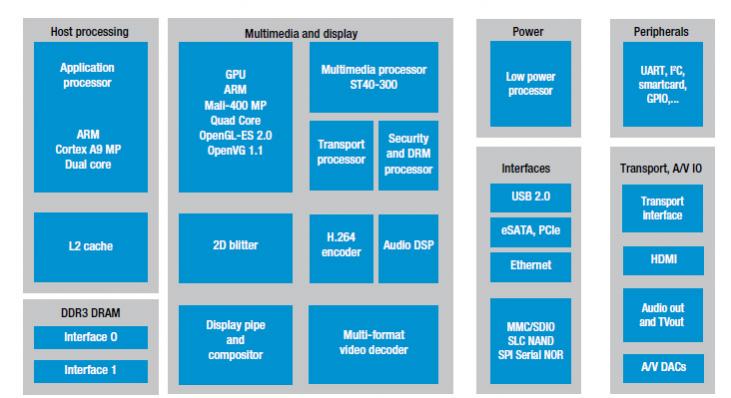

that will be embedded into computer-intensive SOCs serving wireless, set-top-boxes, home gateway markets,

networking and datacenter infrastructure markets…

Orly is ST’s latest generation of HD, AVC set-top box and server decoders for satellite, cable, terrestrial and IP markets

Q: What is your role on the team?

I’m a Processor MicroArchitecture Technical expert. In this context I work on the Power Efficiency optimization of our ARM Cortex A (A9, A15, A57) subsystems focusing on performance improvement and Power reduction.

Q: Tell me about your design challenges.

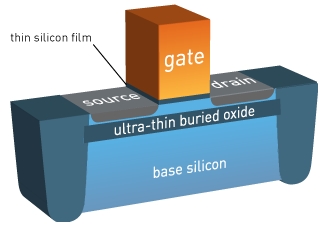

Main challenge in our designs is to combine very aggressive performance targets with very low power consumption on biggest ARM cores through a wide-range DVFS. This is possible thanks to ST technology FDSOI and state-of-the art ST Low Power Architecture and IPs. This is why monitoring Dynamic Power all along our high-end implementation flow is so important.

FDSOI, Source: STMicroelectronics

Q: Which Apache tools are you using?

At RTL level, we are using an Apache tool called PowerArtist.

Q: How do the Apache tools fit into your overall EDA tool flows?

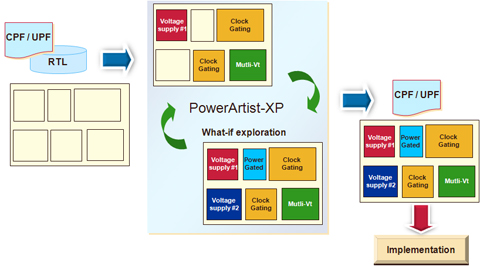

PowerArtist on RTL provides the missing brick between early architectural power evaluation and first power estimates based on netlist gate simulation.

Q: How do the Apache tools help your design team?

PowerArtist tool helps our design team by allowing us to have very early and roughly accurate power data on a full ARM subsystem. It also helps us to develop our power patterns and to identify most suitable power window directly on RTL, avoiding any netlist simulation.

The other benefit is power bug tracking at RTL level and so power convergence along with RTL development

Q: What other approaches did you try before using Apache tools?

The commonly used approach was to estimate power at netlist level, so it was happening too late in our implementation flow.

Q: What was the learning curve like to become proficient with Apache tools?

You need first to generate a PACE model on an existing post-layout netlist. Then, as soon as have you have a PACE model and your clock description, PowerArtist is quite easy to use and we obtained good power figures accuracy without any need of fine tuning of the tool.

Q: What is support like from Apache?

When we have started with the tool we get full support of Apache engineer to generate the PACE model. Then, during power estimates with PowerArtist we get a good support from the Apache team and our requests for improvement have been taken into account by the Apache R&D. So we are happy with Apache’s support.

DAC Presentation

I will start my presentation with an introduction about High Performance Power Efficient ARM Cores implementation within ST and the associated challenge of estimating dynamic power early in the implementation flow. Then I’ll present results obtained when benchmarking PowerArtist tool by measuring accuracy versus signoff power figures on a Dual-cortex A9 subsystem. I will pursue by explaining how we have used PowerArtist tool on a Dual-Cortex A15 subsystem and the different results we have obtained. Finally, I’ll finish my presentation with a conclusion on the benefits of PowerArtist tool.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.