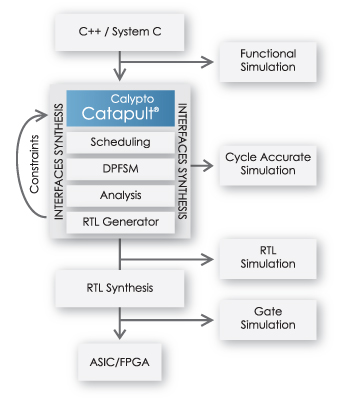

At the end of last week I talked to Sanjiv Kaul, the new CEO of Calypto. Just to give a little background for those that haven’t been following along at home, Calypto was founded to try and solve the very hard problem of sequential logical equivalence checking (mostly by people from the engineering team that I managed at Ambit). SLEC is automatically comparing the C (or SystemC etc) input to high level synthesis (HLS) with the RTL output. They then took this technology and produced a sequential power reduction product, which was a much easier sell since it didn’t depend on the acceptance of HLS, it operated at the RTL level. Meanwhile, over at Mentor they developed an HLS product called Catapult that was having a hard time getting traction without a focused sales force. The Catapult product line and its people were transferred to Calypto in a complicated transaction so now Calypto has 3 product lines:

- SLEC

- PowerPro

- Catapult

HLS has been bouncing along for years with early adopters and a slow adoption. The first product in the space, that was eventually canceled, was Synopsys Behavioral Compiler back in the mid-1990s. A decade ago everyone pretty much assumed that after RTL would come HLS and we’d move up a level. But in fact we switched to IP as a higher-level abstraction. But as IP blocks are now so large individually that we need to improve the productivity of creating them. When Sanjiv has been talking to customers, many are starting to be at that proliferation stage where their initial projects have been a success and now it is time to deploy widely across the company.

“RTL is the new netlist.” The process for getting from RTL to completed physical layout is now getting to be turnkey (of course the people turning the keys would argue it is really hard, and that is true, but it is not really where the value is added in the design). More and more of the differentiation is going on at the IP level and this is the big opportunity for HLS.

Since Catapult has the only SLEC product on the market, Sanjiv feels this means that they are the best positioned. Formal verification techniques tend to be hard to use without guidance from the synthesis tool, but until Catapult moved into Calypto it wasn’t possible to build in appropriate hooks. By more tightly integrating Calypto with both SLEC and with the sequential power reduction, a more powerful product can be made.

In the past, Sanjiv has taken multiple products to a market dominating position, such as PrimeTime or Physical Compiler at Synopsys. Of course he hopes that the magic will work again and feels Calypto is well positioned to be the standard HLS/SLEC tool, the winner in the space. But it is early and there are multiple players. It reminds him of the early days of logic synthesis when companies such as Silc, Trimeter, Mentor/Autologic were also around, before the market standardized on DC.

Calypto is profitable and cash-flow positive (which is actually more important in a startup). They are around 100 people.

There is a webinar coming up on March 26th at 10am Pacific on How to Optimize for Power with High Level Synthesis. More details here.

Share this post via:

The Data Crisis is Unfolding – Are We Ready?