Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock gating, which is combinational power optimization. Combinational in the sense that nothing changes at the register outputs. Years ago, before power was the issue it is today, people were told never to gate the clock. Gating the clock risked race conditions when the signal to gate the clock came to close to the clock transition, and in a way that timing analysis found hard to handle. So if a register did not change under some condition, the value was simply recirculated from the output through a multiplexor. If the multiplexor was 0 a new value was clocked in, if it was 1 then it recirculated. Clearly, from a power point of view, rather than recirculating the existing value and clocking it into the register, it would be much better not to clock the register at all, and this is what clock gating does. Every synthesis tool will do this automatically.

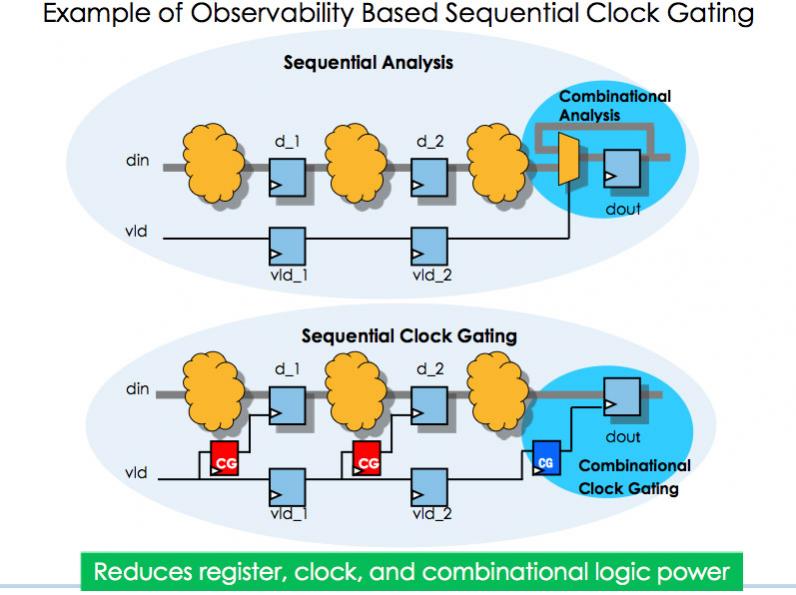

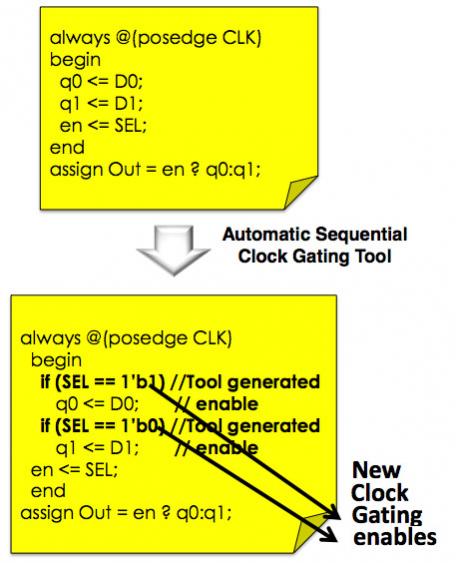

Now, if a register does not clock on this clock cycle and its value is loaded into another register on the next clock cycle, then that can also be suppressed. After all we know the register already contains the correct value. But the analysis required to ensure this is done correctly is quite subtle. As is deducing that if a register is not going to be clocked on this cycle, we don’t care what the value is in the upstream register and so it didn’t need clocking on the previous cycle. Again, this requires reasoning across multiple clock cycles.

Now, if a register does not clock on this clock cycle and its value is loaded into another register on the next clock cycle, then that can also be suppressed. After all we know the register already contains the correct value. But the analysis required to ensure this is done correctly is quite subtle. As is deducing that if a register is not going to be clocked on this cycle, we don’t care what the value is in the upstream register and so it didn’t need clocking on the previous cycle. Again, this requires reasoning across multiple clock cycles.

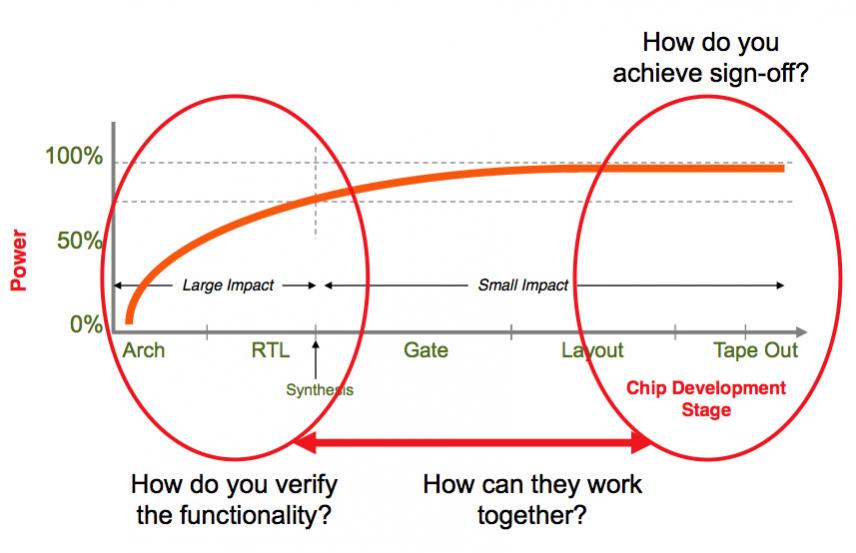

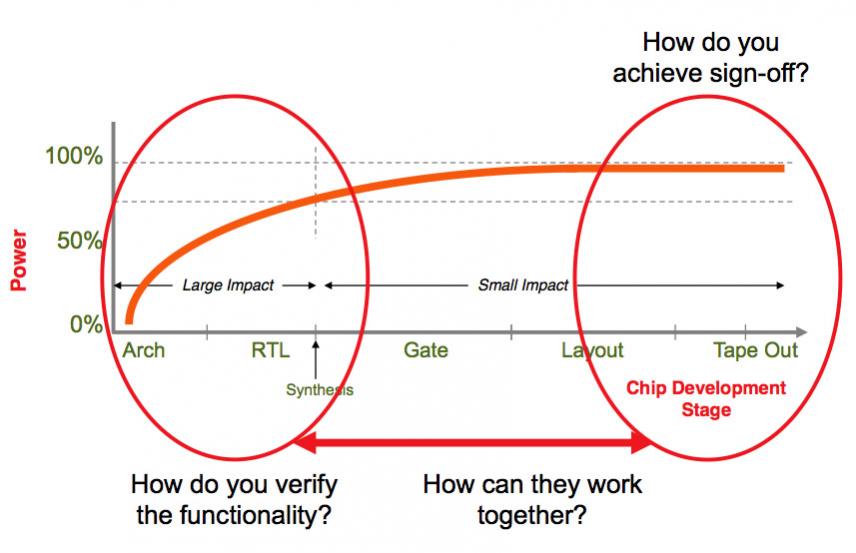

Calypto started out creating technology for this sort of formal analysis. The first application they brought to market was sequential logical equivalence checking (SLEC), formal verification for high level synthesis (or complex manual optimization). But the technology has really come into its own when used for reasoning about power reduction and so reducing power at the RTL level, in the sense that the tool, PowerPro, reads in the RTL and writes out a new RTL that has the same behavior at the outputs but consumes less power.

There are some subtleties about getting the most out of PowerPro. For example, if you have a datapath and control logic and try and reduce the power on the datapath alone you are not going to get very far. Similarly, if you have a clock that is simply another clock divided down, but you don’t tell the tool, you similarly will not get any reduction since PowerPro has to assume that different clocks are completely asynchronous to be safe.

Anyway, PowerPro (and SLEC) are unique tools. This sort of sequential analysis is really really hard and no other company seems to have mastered it. So this webinar isn’t a me-too webinar that is just the same as ones from other companies, this is the experts on sequential power optimization going into a reasonable amount of depth on what the technology is capable of.

The webinar will be presented by Abishek Ranjan, a senior director of engineering at Calypto. It is on Tuesday December 4th at 11am.

More details about the webinar, and to register, are here.

Share this post via:

The Data Crisis is Unfolding – Are We Ready?