If we look at SoC design evolution, we have certainly successfully passed several steps: from transistor by transistor IC design using Calma up to design methodology based on the integration of 500K + gates IP like PCIe gen-3 Controller, one out of several dozens of IP integrated in today’ SoC for Set-Top-Box or Wireless Application Processor. Are we naïve if we think the next step should be subsystem IP? It would really make sense to use an IP aggregation, organized in such a way that it could support a specific application!

The list of benefits is long: at first, it will certainly speed up the design integration phase, thus offering a better Time-To-Market. Above mentioned SoC, designed on 28nm technology requires an investment in the $40M to $80M, and they have to hit the market on line with the end user expectations (better Video quality, lower power consumption offering longer time between batteries charging, higher data throughput allowing faster data download, and so on). Being able to deliver the right SoC just in time will allow to sell at the right price, offering enough gross profit margins (GPM), so the chip maker can satisfy investors and continue to invest and gain market share. Missing the market window could put the product line, if not the overall company, at risk.

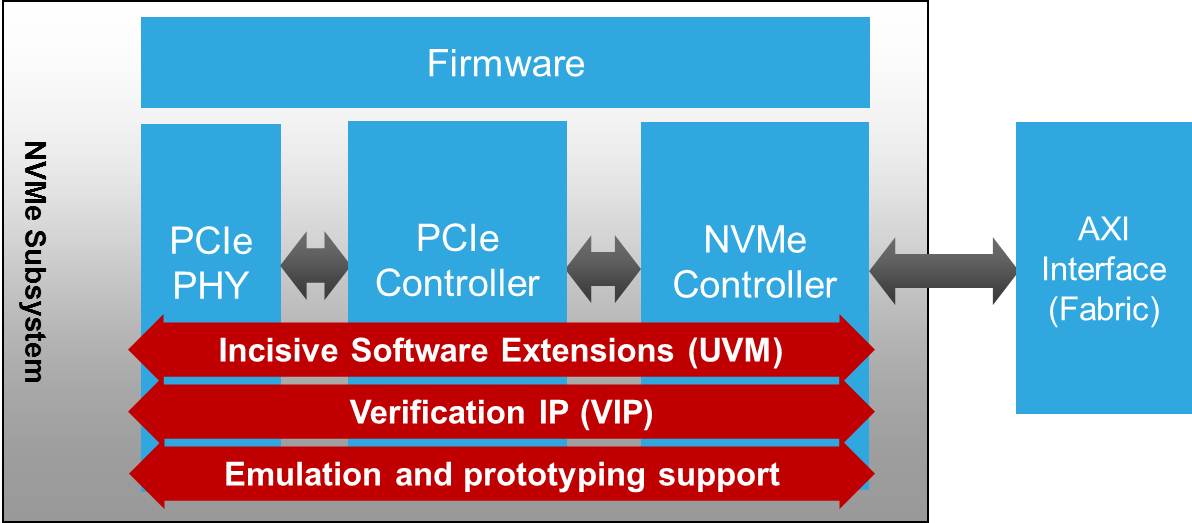

A subsystem IP based approach will also speed up the software development and validation phase: if the IP provider is able to propose the right tools, like the associated Verification IP (VIP), the software development tools tightly coupled with the subsystem description model, as well as proper emulation and prototyping support, the (S/W & H/W) development team can simply go faster. Good for the TTM, allowing hitting the market window, good again for the GPM!

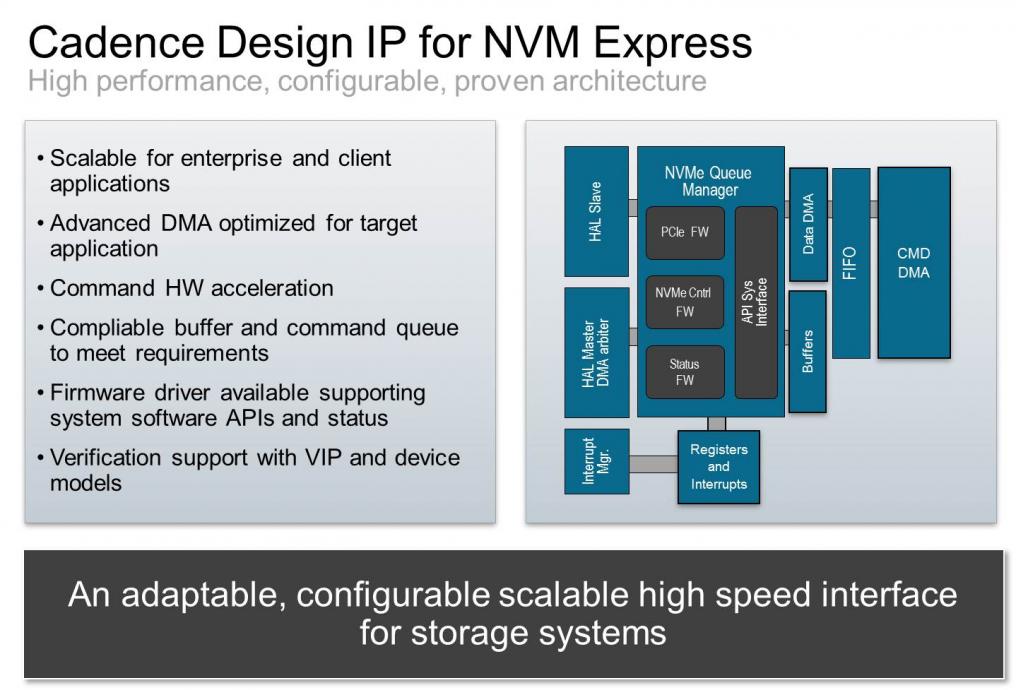

The Cadence Design IP for NVM Express is the industry’s first IP subsystem for the development of SoCs supporting the NVM Express 1.0c standard, an interface technology used in the rapidly growing solid-state drive (SSD) market, and, to my opinion, an important step on the above mentioned SoC evolution, as this solution includes:

- PCIe 8GT/s PHY IP

- NVMe and PCIe Controller IP combine (reducing engineering effort while optimizing overall solution)

- Firmware accelerates the HW/SW integration effort

- Capabilities from VIP, UVM and IP products along with,

- Fast prototyping and virtualized software products to simplify the design process

Cadence has not chosen NVM Express by chance, in fact the Denali acquisition has bring to Cadence IP port-folio both the PCIe Controller IP product and the Nand Flash Controller (Non Volatile Memory = NVM) IP product, complemented with a PHY IP coming from internal source.

The move from HDD to SSD is good news for end users (including myself, I definitely vote for HDD replacement by SSD!) and the move from SATA interface to PCI Express is also good news: PCI Express offers much more features than SATA (Virtualization, High Outstanding request count, to name a very few of them), and also offers scalability, that SATA does not, and configurability, which is good for a subsystem IP, as Cadence potential customers will need to differentiate each other’s. I may come back in a later blog and talk about the –potential- drawbacks with subsystem IP, but I am intimately convinced that the benefits coming from this type of IP solution are higher, and that the SoC evolution will go on.

Eric Estevefrom IPNEST–

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.