Intro

Most EDA parasitic extraction tools have built-in RC reduction with no user control however at DAC I learned how Edxact offers a stand-along RLCK reduction tool for IC designers that want more control over what happens to their extracted netlists.

Daniel Borgraeve (on right)

Notes

Edxact

– Started seven years ago

– Fifteen people in the company

– Based in France

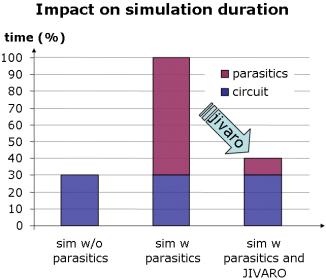

– Jivaro: RLCK reduction (RLCC) with user control of results

o Many algorithms to choose from

o Used by Aglient in their GoldenGate tool (RF Simulator)

o Used by Intel

o About 25 customers world wide (Asia, Japan, Korea, US)

o Part of TSMC AMS Reference flow 2.0

o Pricing starts at $100K per license per year

– Comanche:

o Read parasitic

o Create R values point to point, calculate delays

o CAD developers can compare two netlists (Golden versus some extraction tool)

o Parasitic analysis platform

o Used by: AMD, ST Ericsson

o Pricing starts at $100K per license per year

– Partners

o Altos (Library Characterization, used Jivaro)

o Cadence (Integrated into Virtuoso)

o SpringSoft (Integrated into Laker, can annotate parasitic into Laker)

o Mentor (read DSPF, Eldo formats)

o Synopsps (support Star RC and HSPICE syntax)

o TSMC – part of AMS Reference flow

– Runs on: Solaris, Linux, Mac

Summary

If you want more control while reducing RCLK netlists then consider looking at Edxact tools.

ASML- Soft revenues & Orders – But…China 49% – Memory Improving