At DAC this year there was a presentation from Samsung titled, “Profile-based Architecture Power Modeling Methodology for AP/SoC Product”. I’ve been using Samsung Smart Phones for the past four generations, so was very curious about how they have managed to improve the average battery life from less than one business day to about 1.5 days now while dramatically increasing both screen size and CPU/GPU metrics.

Jongho Kim from Samsung was the presenter and he has a Master’s Degree in Electrical Engineering, then working at Samsung since 2008.

Jongho Kim, Samsung Electronics

Power Challenge

When I moved from a feature phone to my first smart phone I was shocked at how short-lived the new device was, because my feature phone lasted 7 days on a single charge while the smart phone didn’t make it through one business day. The consumer convenience of longer-lasting life on a battery charge is a big deal.

Approaches to Early Power Estimation

You could just use an Excel spreadsheet at the earliest stage of design a mobile SoC and try to estimate power for every IP block under various use scenarios. The down-side of this Excel approach is that it’s not scalable, not easily shared within the design team, and is not structured.

To automate any power estimation approach you first need structure and then a methodology. An ideal power estimation platform would:

- Allow power models for all IP blocks, at any stage of design

- Run all use-case scenarios, quickly

- Support a what-if analysis to optimize complex power management options

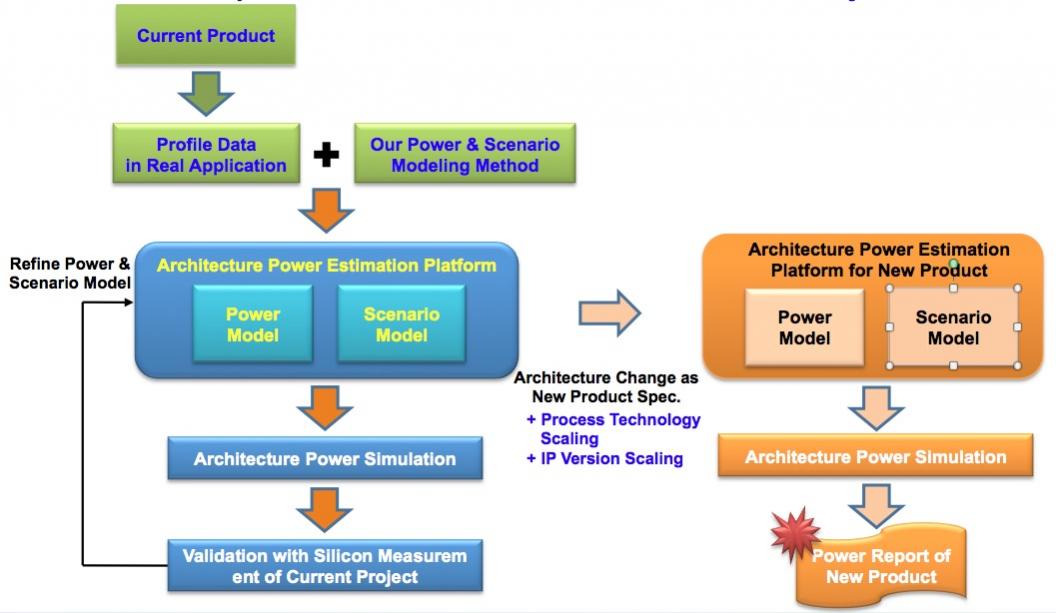

Even with such a platform you still have work ahead of you, like: building the models, proving correlation between the model and silicon, and re-using power efforts from past projects. Here’s the power estimation flow used by Kim’s group at Samsung:

To start out in this flow they took an existing product, shown in the the green boxes, and then created a power profile based on actual use: playing MP3, Camcorder, Video playback, 3D gaming, LCD on idle, etc. Once you have models then you can start to generate power numbers and compare them with actual silicon as shown in the blue boxes. The silicon results feed back into the models to dial in the accuracy. Finally, you can use the power and scenario models from an existing product into your new product development, shown in the orange boxes.

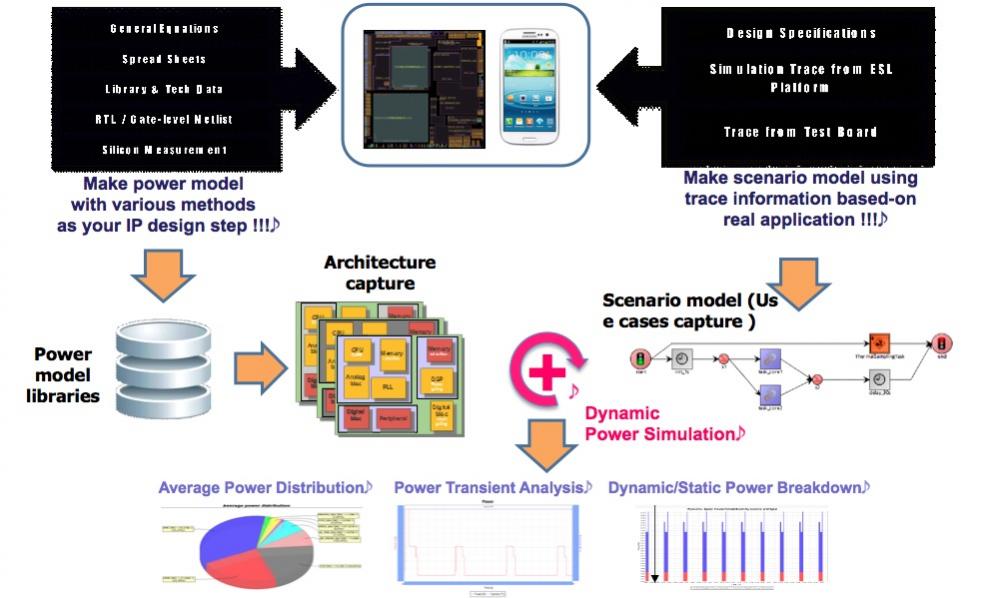

Samsung engineers used an EDA tool from Docea Powercalled Aceplorer to run a dynamic power simulation for what-if analysis using the power and scenario models.

Each IP block on the SoC has a power model that was built in a variety of ways:

- New IP blocks without RTL yet used general equations, spreadsheets or library technology data.

- IP blocks with RTL or a netlist used gate-level power estimates.

- Re-used IP blocks used silicon-correlated power data.

This methodology allowed Samsung to get a very early power estimate on new SoC designs. Scenario models contain info on power versus: Voltage, Frequency, State. The three charts at the bottom are outputs from Aceplorer:

- Average Power Distribution

- Power Transient Analysis

- Dynamic/Static Power Breakdown

Internal EDA Tools

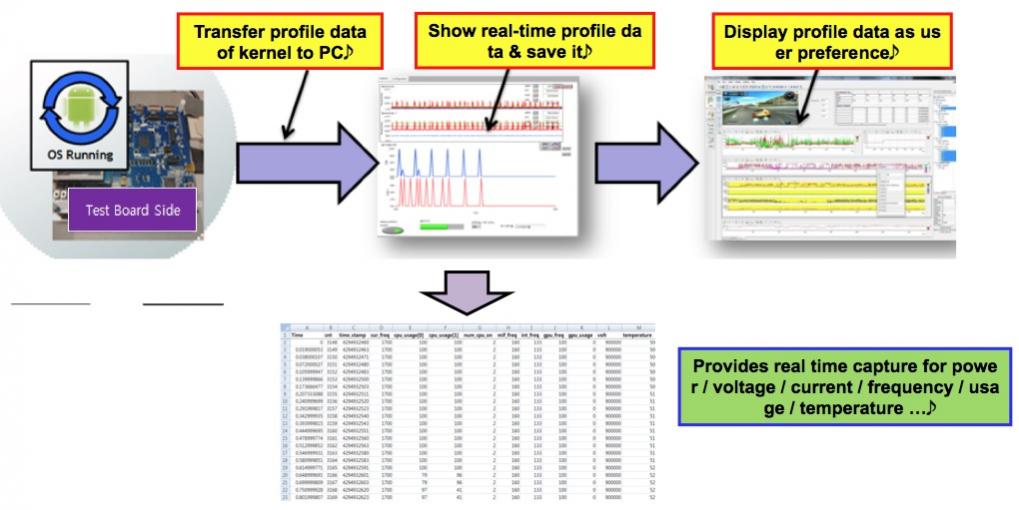

Samsung developed their own performance profiler tool as part of their power flow in creating the power scenario models used in Aceplorer.

The power models need to capture details like:

- IP State: Active, Idle, Clock Gating, Power Gating

- Dynamic power: Voltage, Frequency, Workload

- Static Power: Voltage, Temperature

Example Model

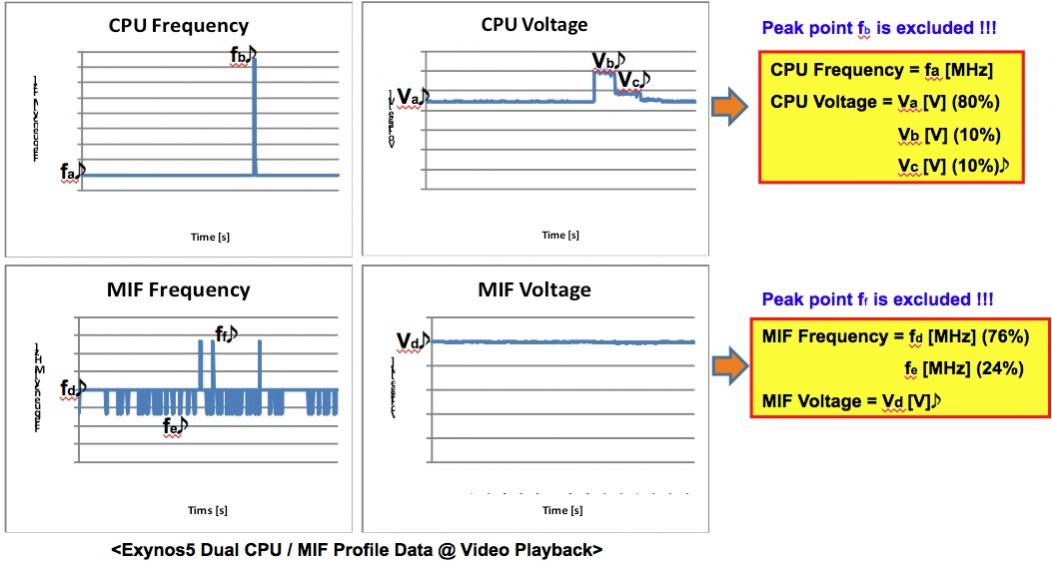

An example of a power scenario model for the Exynos5 Dual CPU is shown below:

Power Model Accuracy versus Silicon

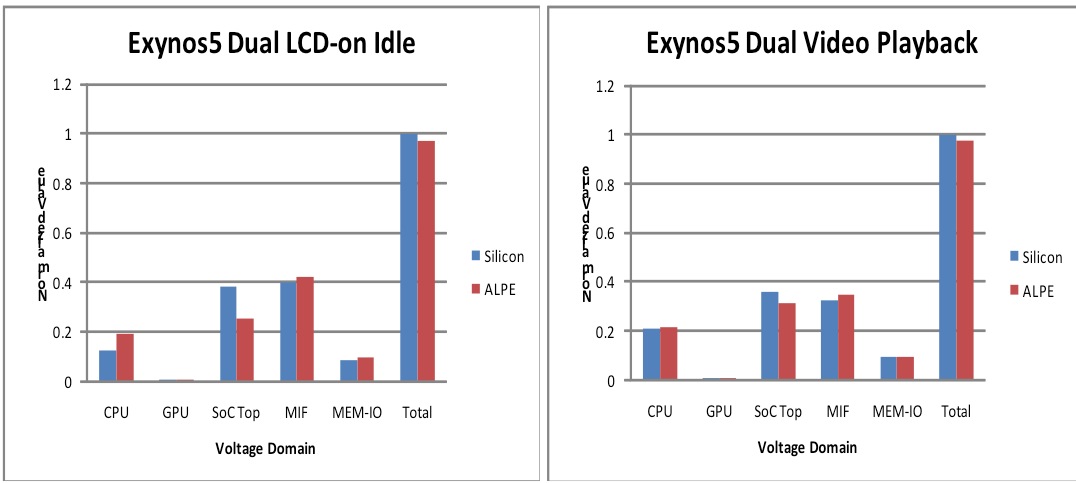

Silicon is the ultimate reference for measurement comparisons versus estimation, so the Samsung engineers compared silicon measurements on the Exynos 5 Dual Power chip versus their Architecture Level Power Estimation (ALPE):

The estimated power values shown in Red correlate adequately with the silicon measurements shown in Blue, with a difference of less than 10%.

Summary

Consumer electronic companies like Samsung have successfully used an Architectural Level Power Estimation methodology on mobile SoC designs to optimize for power. For further reading:

lang: en_US

Share this post via:

Real men have fabs!