Berkeley Design Automation today announced the first silicon-accurate circuit simulation for mega-scale arrays like memories and CMOS image sensors. If this tool lives up to its claims, it is going to be a big deal for FinFET-based circuits, Memory designers are rightly worried about having the accuracy necessary to include detailed physical effects—like all of the new parasitics and variation due to those models.

Today’s memory simulators are traditional fastSPICE tools that are architected to partition circuits, into smaller problems that they solve independently and tie together with an event simulator. This approach inherently introduces at least a few percentage points of inaccuracy. Adding to that, fastSPICE tools utilize table-lookup models which likewise sacrifice accuracy for performance. The result is simulators that are much higher capacity and faster than SPICE, but that require tuning per partition, tuning for different types of simulations (e.g., critical-path timing versus power), tuning for different configurations, and tuning for different modes and corners. Even with all of this tuning, the accuracy of the results is always suspect. While it’s possible to calibrate fastSPICE simulators against SPICE simulators on smaller circuits, because of partitioning and other simplifications, the fastSPICE simulator accuracy for a given circuit does not hold as that is integrated into a much larger circuit.

BDA developed AFS Mega the hard way—by extending its existing foundry-certified AFS Platform to meet the performance, capacity, and design flow requirements of memory simulations without altering the architecture or core engine. That’s right. AFS Mega is just the biggest, baddest SPICE simulator ever. It does not partition circuits, it does not have an event simulator, and it does not use table look-up models.

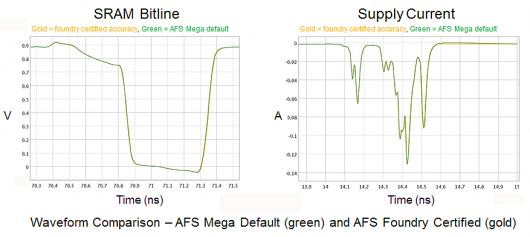

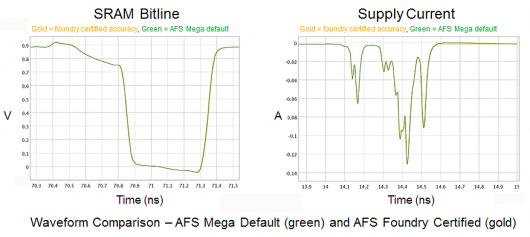

To be fair, AFS Mega defaults to a few simplifications that can deliver an additional 10x speed on mega-array-based circuits while staying within a few tenths of a percent inaccuracy. That is more than an order-of-magnitude better accuracy than is possible today with even the most diligent tuning of traditional fastSPICE tools—and BDA claims AFS Mega is meeting or beating them in terms of performance. That’s out of the box or with a few global settings.

Want more accuracy? BDA says “no problem.” It will cost you some runtime, but the tool can run’s today’s full macro embedded SRAMs with foundry certified accuracy—accuracy that the company is now certifying at FinFET-based nodes at the world’s four largest foundries.

BDA is not announcing that AFS Mega works with its other AFS Platform capabilities, e.g., AFS AMS or its newly announced Analog Characterization Environment (ACE), but as part of the AFS Platform, support for such capabilities has to be relatively straightforward.

Is AFS Mega real? Of course it is, I’m an SRAM guy and I worked with BDA on this product so I know. But don’t take my word for it, stay tuned for endorsements from the top SRAM suppliers around the world.

lang: en_US

Share this post via:

Real men have fabs!