I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be gated on the following clock cycle. Of course what often happens is that a register remains unchanged for many clock cycles. Often the downstream register is not just depending on a single upstream register but multiple ones (for example, the output from an adder) in which case care needs to be taken to ensure the downstream register is clocked whenever its input changes.

The other approach, which is a bit trickier, is to propagate upstream. If a register is not clocked on this clock-cycle then registers that feed it do not need to be correct on the previous clock cycle because the value is not going to be used. It is harder to figure out how to create signals a clock cycle earlier though since there may not be an appropriate signal available.

Observability Don’t Care (ODC) is when several registers feed into a mux. Given the value of the mux only one of the registers is actually required to have the correct value and the others don’t need to be up to date since the values will be blocked by the mux.

Another approach, which is not sequential, that is sometimes appropriate is to compare the input and output of a register. This only makes sense if the input is stable over long periods of clock cycles. If the registers are large the comparison can generate huge xor-gates, but splitting these registers often yields good results. The comparison can be used to inhibit clocking downstream registers when the register is not changing its value.

There are also reduction approaches associated with memories. There are huge power savings possible from looking at address/data stability and inhibiting unnecessary memory operations.

PowerArtist works by analyzing the design, looking at the topology and doing power analysis. It then makes judgements on how much power will be saved and thus which changes to the design make sense. If registers have many bits then the power saved by not clocking them can be large, and so can justify overhead (in power and area) to calculate the clock gating signals.

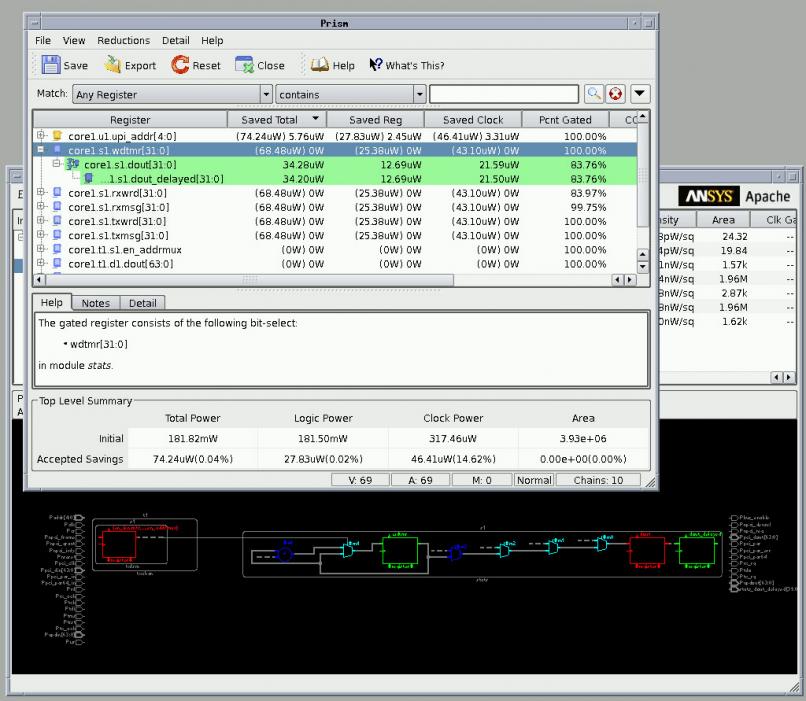

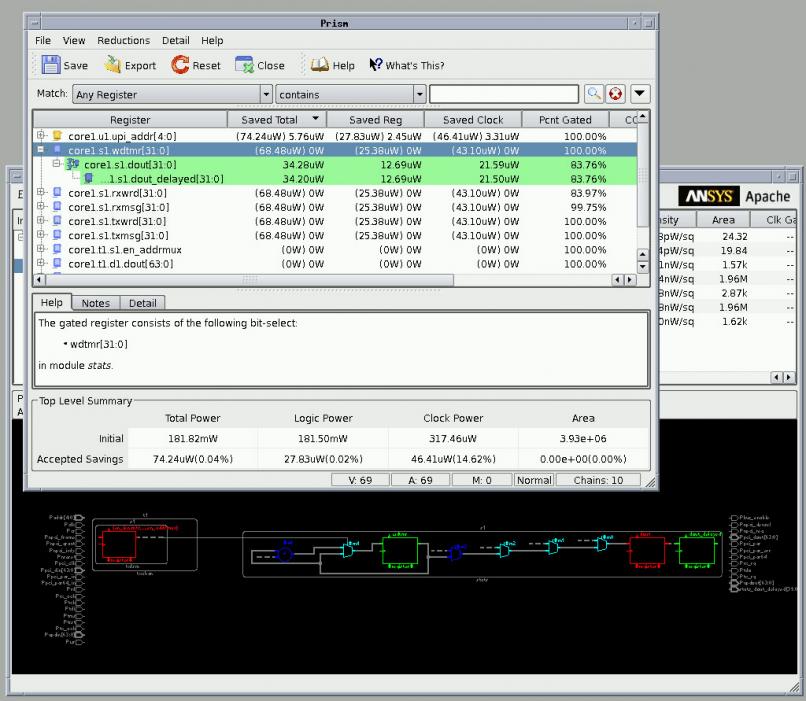

The user interface (see the picture above) to the PowerArtist sequential reduction browser highlights registers that can be clock-gated and the power that can be saved. These same registers can also be seen traced in the schematic view

Coming in part II: RTL Power Model (RPM) and Power Artist Calibration Estimator (PACE)

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.