At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

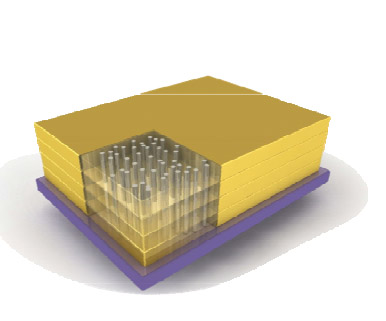

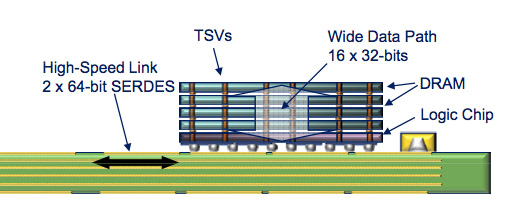

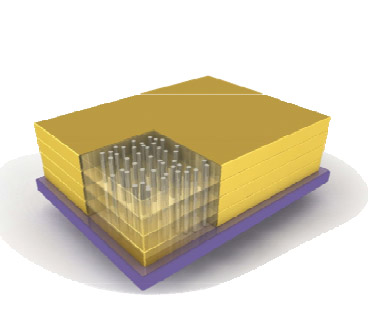

Micron have a Hybrid Memory Cube (HMC). Bandwidth to the memory is 128GB/s (1 terabit per second). Each die in the stack is divided up into partitions, each of which is a 2-bank autonomous memory element. In turn, these are grouped in the vertical direction into “vaults” that consist of the same partition on each die all linked up together using through-silicon-vias (TSVs). In turn, the memory die are stacked on top of a single logic die to form the whole cube, with fully integrated DRAM and logic.

Micron have a Hybrid Memory Cube (HMC). Bandwidth to the memory is 128GB/s (1 terabit per second). Each die in the stack is divided up into partitions, each of which is a 2-bank autonomous memory element. In turn, these are grouped in the vertical direction into “vaults” that consist of the same partition on each die all linked up together using through-silicon-vias (TSVs). In turn, the memory die are stacked on top of a single logic die to form the whole cube, with fully integrated DRAM and logic.

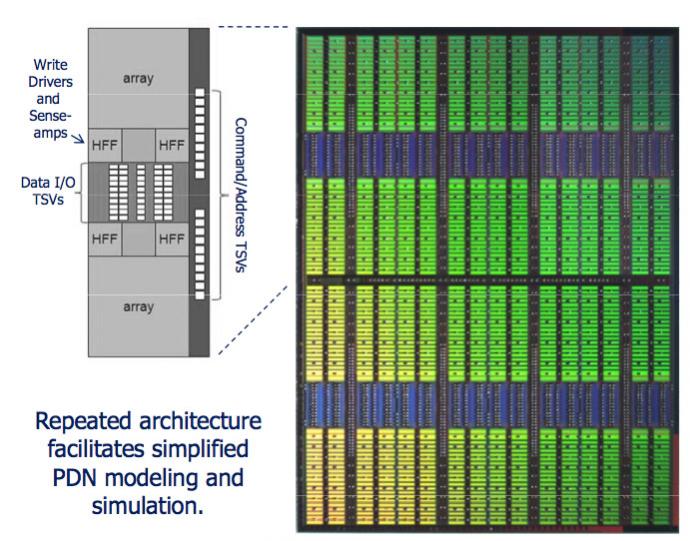

This way of dividing up the cube is also used to divide up the simulation. Initially partition level simulations are used to capture general noise to timing sensitivity. Multi-partition simulations (same die) capture inter-partition noise coupling, and vault level (vertical slice) capture die to die noise coupling. Finally, cube level simulations capture the impact of system power delivery network (PDN), resonance etc. The fact that there is so much repeated in the architecture make this very hierarchical approach viable.

At the partition level, simulation focused on power-grid impedance analysis, voltage drop analysis, full spice-level simulation with the power grid and decoupling all modeled. Apache’s Totem static analysis was used to correct layout and to validate that the silicon and the model matched.

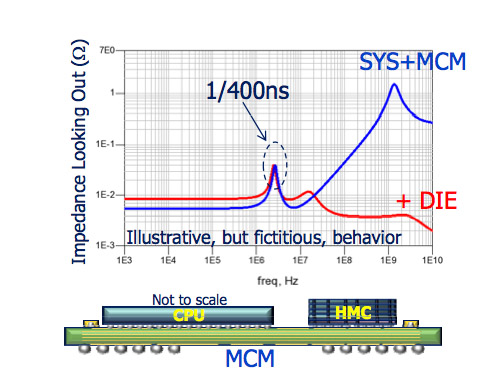

At the vault level (multi die) Apache’s chip-power-model (CPM) was used to create dummy layers and the simulation focused on ensuring that layers were adequately isolated from noise. Then at the level of the system PDN the focus was on noise and resonance and adequacy of decoupling.

Takeaways from modeling the hybrid memory cube:

- complexity is a function of how tightly coupled different parts of the system are and how much concurrent activity is allowed

- physically partitioning the device simplifies design, modeling and simulation

- 3D challenges must be overcome in parallel.

The Micron presentation is here in Apache’s CPS microsite.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.