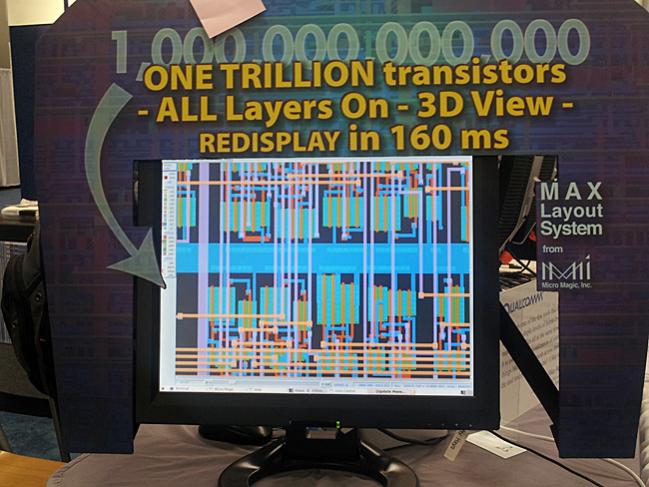

There are only a handful of billion transistor IC designs in existence today, so when an EDA company touts 1 trillion transistor IC layout editing then I take notice. This year at DAC I met with Katherine Hayes and Karen Mangum of Micro Magic to get an update on their IC layout tools.

2011 a 3D floor planner, auto placement of TSVs.

2012 MAX-3D Path Finder – layout tool for 3D designer, stacked dies or interposer design (becoming more popular). Layout can be done in another tool like Virtuoso, read in the GDS II or OA db to Micro Magic tool.

– can read in a Verilog netlist, start floorplanning and visualize where TSVs will be located. Use MM extraction tool for early what-if analysis.

– Tezzaron Semi has used MAX 3D to tapeout over 100 chips so far, some up to 20 GB GDSII files (up to 5 layers of IC dies).

-Qualcomm uses MAX 3D tools as well.

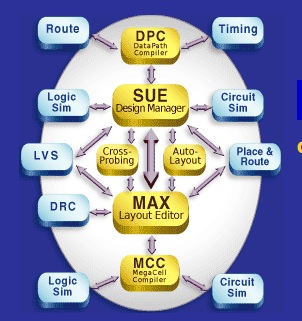

MAX 3D Design Suite – SUE (Schematic User Environment), DPC (Datapath and cell placement), MAX-3D PF (layout editor with 3D or 2.5D with interposer), Path Finder, TSV Placer. Priced at $(see your sales rep), or call the factory.

Trillion transistor demo design being show (also from last year).

Summary

Micro Magic has some impressive IC layout technology and is aimed at the growing market for 3D layout tools. To take their EDA business to the next level we need to see some more recent customer success stories and tool adoption.

The Data Crisis is Unfolding – Are We Ready?